Временные диаграммы

Скважность импульсов

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Назначение, схема и принцип работы JK-триггер

Главная Избранные Случайная статья Познавательные Новые добавления Обратная связь FAQ

⇐ ПредыдущаяСтр 6 из 9Следующая ⇒

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J | K | Q(t) | Q(t+1) |

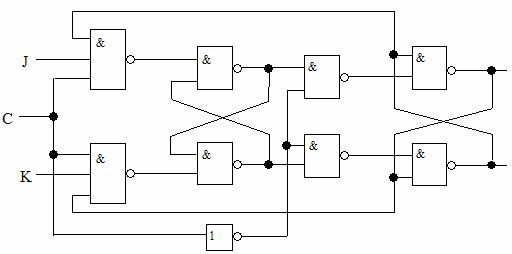

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump

— прыжок) аналогичен входуS у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входуR у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронтуимпульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и Kлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К.

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом С

Назначение, схема и принцип работы счетчиков импульсов.

Электронный счетчик импульсов предназначен для подсчета количества импульсов, поступающих с измерительных датчиков на счетные входы (или один счетный вход) счетчика импульсов и пересчета их в требуемые физические единицы измерения путем умножения на заданный множитель (например, в метры, литры, штуки, килограммы и т. д.); подсчета суммарной выработки за смену, сутки, неделю, месяц и т. д.; управления исполнительными механизмами одним или несколькими дискретными выходами (чаще всего, в счетчиках импульсов в качестве дискретного выхода используется реле или оптопара).

Как правило, в качестве датчика применяется механический прерыватель илииндуктивный датчик (бесконтактный датчик) или энкодер.

Электронные счетчики импульсов могут иметь высокую степень защиты IP (степень защиты оболочки) от пыли и воды (например, IP65).

Счетчик импульсов (некоторые модели) может иметь встроенную функцию тахометра илирасходомера.

Электронные счетчики импульсов сохраняют результат измерений при исчезновении напряжения питания в течение неограниченного периода времени в энергонезависимой памяти (EEPROM). После возврата напряжения питания счет импульсов продолжается, начиная с сохраненного значения; некоторые модели счетчиков импульсов индицируют факт пропадания напряжения питания во время работы.

Некоторые модели имеют интерфейс для подключения к сети или компьютеру (например, RS485, RS232, CAN), а также аналоговый выход ЦАП, который может быть использован как для передачи информации другим контрольно-измерительным приборам управления исполнительными механизмами (например, электроприводом).

Кроме того, счётчики импульсов классифицируют по направлению счета (режиму работы):

суммирующие счетчики импульсов;

вычитающие счетчики импульсов;

реверсивные счетчики импульсов.

Импульсы от энкодера с определением направления вращения

Реверсивные счетчики импульсов чаще всего используются при работе с 2-х канальнымиэнкодерами или с двумя индуктивными датчиками, при этом:

автоматически счетчиком импульсов определяется направление вращения энкодера;

происходит увеличение в 4 раза разрешающей способности энкодера, то есть 1 полный импульс c энкодера счетчик импульсов превращает в 4 инкремента (см. рис. поясняющий работу счетчика импульсов в реверсивном режиме).

⇐ Предыдущая6Следующая ⇒

Универсальный триггер

JK-триггер

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f имеет вид:

Таблица истинности JK-триггера:

| J | K | Q(t) | Q(t+1) |

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

| KQ(t) |

| J |

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Лекция 6. Структурная схема конечного автомата

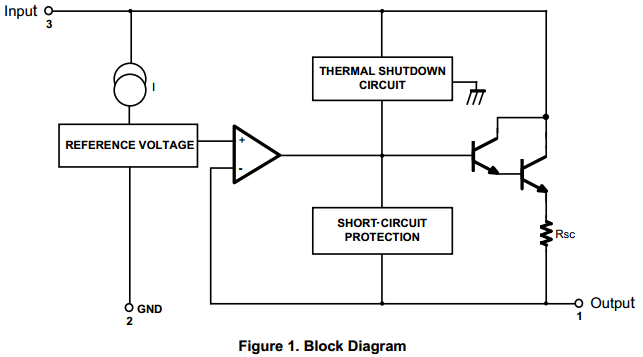

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

| __ | ||

| Qa = | Q | ,еслиa=0 |

| Q | ,еслиa=1 |

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Синхронный RS-триггер

Схема асинхронного RS-триггера проста, но за это приходится заплатить целым рядом недостатков: наличие запрещенного состояния, установка 0 и 1 по отдельным линиям отсутствие синхронизации, низкая помехоустойчивость. Эти недостатки частично устраняются в синхронном RS-триггере, который представляет собой асинхронный RS-триггер к которому добавлена схема синхронизации.

В целом работа данного триггера аналогична, с той поправкой, что при наличии на входе синхронизации низкого логического уровня триггер хранит предыдущее состояние, не реагируя на сигналы по входным линиям, т.е. в этот момент он как минимум гораздо более помехоустойчив.

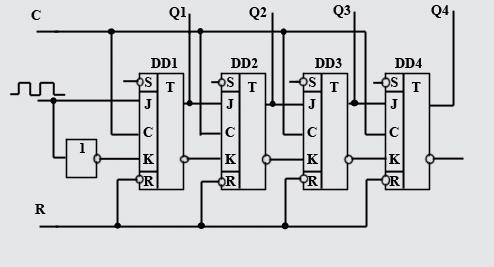

Для использования триггеров в реальных счетных устройствах, необходимо иметь возможность дополнительного управления их состояниями — предустановки, обнуления, активации с помощью счетного тактового импульса. Что бы осуществить эту операцию в схему счетного триггера добавляется еще три входа. PRESET(PR) — восстанавливает на выходе триггера состояние 1, а СLEAR(CL) — состояние 0. С помощью тактового входа Т осуществляется общая синхронизация триггера, относительно других элементов схемы счетного устройства. Импульс поступающий на счетный вход D меняет состояние триггера, только при наличии 1 на тактовом входе.

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние

- 1 RS — триггер

- 1.1 Классическая реализация RS-триггера

- 1.2 Временные диаграммы RS-триггера

- 1.3 Другая реализация RS-триггера

- 2 Синхронный RS-триггер

- 3 Синхронный JK-триггер

- 3.1 Схема JK-триггера

- 3.2 Конкретная реализация синхронного JK-триггера

- 4 D-триггер

- 5 Т-триггер

- 6 Двухступенчатые триггеры

- 6.1 Двухступенчатый синхронный RS-триггер

- 6.2 Двухступенчатый D-триггер

- 6.3 Двухступенчатый JK-триггер

- 7 Универсальные триггеры

- 8 Ступенчатый D-триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Триггеры. RS-триггеры. Асинхронный RS-триггер с инверсными входами

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

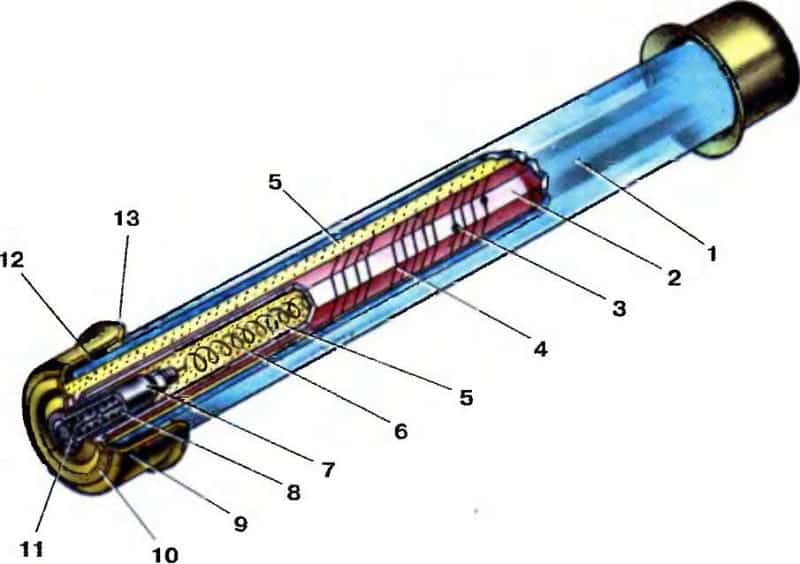

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер имеет два выхода: прямой Q

и инверсный. Состояние триггера определяют по значению сигнала на прямом выходеQ. Значения сигналов на прямом и инверсном выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

1.RS-триггеры ‘АсинхронныеRS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. АсинхронныеRS -триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS

-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входаS иR.. По входуS триггер устанавливается в состояниеQ =1( =0), по входуR— в состояниеQ =0(= 1). В зависимости от логической структуры асинхронныеRS -триггеры бывают с прямыми либо инверсными входами и могут строиться на двух логических элементах: 2ИЛИ-НЕ — триггер с прямыми входами; или на элементах 2И-НЕ — триггер с инверсными входами.

АсинхронныйRS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q

и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

Временные диаграммы, характеризующие работу асинхронного RS

-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R

=S =0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (R и S) приводит к неопределенности. На обоих выходахQи появляются единицы, а после отключения входов (S=R=0) может установиться любое состояние

JK-триггер. Принцип работы, фунцкциональные схемы, таблицы истинности

Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

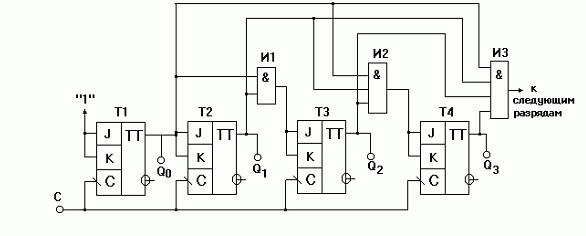

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов.

JK-триггер

Рассмотрим схему простейшего JK-триггера. От RST-триггера он отличается двумя обратными связями, которые устраняют неопределенность в таблице состояний. Назначение входов J и К такое же, как и входов R и S (сброс и установка). Буквы J и К были выбраны в свое время авторами как соседние в алфавите (сравните К и S).

Если входы J, C и К объединить, то получим схему Т-триггера, а если входы элементов ТТЛ DD1.1 и DD1.2 равноправны. Следовательно, как только на объединенный вход С поступит напряжение высокого уровня (после низкого), состояние выходов Q и Q изменится. Вход С можно от общей точки отключить, и в этом случае входная комбинация J = H и К = В переключит триггер: объединенные входы J и К выступят в роли отомкнутого входа С. Таким образом, неопределенности на выходах триггера при обоих высоких входных уровнях в JK-триггере не существует.

Рассмотрим схему управления JK-триггером и его таблицу состояний, в которой две графы: установлено (делается в момент tn) и записано (анализируется состояние выходов после прихода тактового перепада в последующий момент tn+1). При входных сигналах J = H и К = Н состояние выходов не меняется, оно сохраняется таким, каким было в момент установки tn. Напомним, что напряжение низкого уровня на одном входе элемента ТТЛ отменяет прохождение сигналов от других его входов и удерживает выходной сигнал на высоком уровне.

Когда через входы J и К в момент tn загружаем взаимно противоположные уровни, то в последующий момент tn+1 выходы JК-триггера устанавливаются в такие же состояния, как и RS-триггер. Последняя строка таблицы отображает, что при подаче на входы J и К одновременно напряжений высокого уровня (входы можно просто соединить), триггер перебрасывается, переходит в состояние, противоположное предыдущему. Например, если было Qn = B; Qn = Н, то станет Qn+1 = Н и Qn+1 = В

Двухфазный способ управления полным тактовым импульсом С применяется и для двухступенчатых JK-триггеров . Этот триггер, как и простой JK-триггер, имеет обратные связи с выходов на входы, исключающие неопределенное логическое состояние. Схема простейшего двухступенчатого JK-триггера показана на рисунке. Защелка ТМ состоит из элементов DD1.2 и DD1.3. Элементы DD1.1 и DD1.4 — входные ключи с которых снимается сигнал C для управления ТП, защелка RS которого построена на элементах DD1.7 и DD1.8. Сигналы управления подаются на ТП через DD1.5 и DD1.6. Триггер может иметь вход общего сброса данных R, который для этой схемы иногда в литературе называют сlеаr. Многие JK-триггеры имеют также вход предварительной установки S (другое название preset), симметричный входу R, что создает дополнительные входы у элементов DD1,1, DD1.2 и DD1.7.

Рассмотрим осциллограмму переключающего импульса, на которой отмечены этапы работы составного триггера. В момент t1 ТП изолирован от ТМ; в момент t2 разрешается прием данных входами TM. С приходом отрицательного перепада импульса в момент t3 запрещается прием данных входами ТМ, а в момент t4 заканчивается перенос данных из ТМ в ТП. Таким образом, замечательное свойство двухфазного управления состоит в том, что входы приема данных за период тактового импульса, т.е. во время загрузки 1 бита информации, не имеют сквозной связи с выходными цепями. Изоляция входов и выходов обеспечивает устойчивое переключение сложного триггера, если частота тактОвых импульсов нестабильна (дрожит).

Вход

Выход

J

K

C

Q

Q

Н

Н

Н

Н,В

В,Н

В

В

В

В,Н

Н,В

Установлено

Записано

J

K

Qn+1

Qn+1

Н

Н

Без изменений

Qn

Qn

Н

В

Н

В

В

Н

В

Н

В

В

Переброс

Qn

Qn