Значение слова триггер

(англ. trigger), спусковое устройство ( спусковая схема ), которое может сколь угодно долго находиться в одном из двух (реже многих) состояний устойчивого равновесия и скачкообразно переключаться из одного состояния в другое под действием внешнего сигнала. Т. имеет два выхода: основной и инверсный. Каждому состоянию Т. соответствуют определённые сигналы на его выходах, отличающиеся своим уровнем. В одном состоянии на основном выходе Т. формируется сигнал высокого уровня, а на инверсном ≈ низкого; в др. состоянии, наоборот, сигналы высокого и низкого уровней формируются соответственно на инверсном и основном выходах. Т. характеризуется следующими важнейшими параметрами: быстродействием, временем срабатывания, уровнями входных и выходных сигналов. Быстродействие Т. определяется как максимальное возможное число переключений в единицу времени. Время срабатывания определяется временем перехода Т. из одного состояния в другое и характеризует задержку выходного сигнала Т. относительно входного. Под уровнем входного сигнала понимают минимальное значение сигнала, необходимое для переключения Т. Уровень выходного сигнала у большинства Т. не ниже уровня входного сигнала, чем обеспечивается возможность их последовательного соединения без промежуточного усиления.

Наибольшее распространение получили электронные Т., выполненные на электронных лампах, газоразрядных приборах, полупроводниковых диодах, транзисторах разных типов и особенно на интегральных микросхемах; иногда применяются также Т. на магнитных элементах, элементах пневмо- и гидроавтоматики и др. По характеру входных сигналов различают Т. с потенциальными входами (прямым и инверсным) и динамическими входами (также прямым и инверсным). Т. с потенциальными входами реагируют на сигнал высокого уровня на прямом входе и низкого уровня на инверсном входе. Т. с динамическими входами реагируют на перепады (изменения уровня) входных сигналов: положительный на прямом входе и отрицательный на инверсном.

══Наиболее часто применяют: Т. со счётным входом (Т-триггер), который изменяет своё состояние на противоположное с каждым входным сигналом; Т. с двумя установочными входами (R ≈ S-триггер), изменяющий своё состояние только при воздействии управляющего сигнала на определённый вход (R-или S-вход), причём повторное воздействие сигнала на тот же вход Т. не изменяет его состояния; универсальный Т. (J ≈ K-триггер), обладающий свойствами Т-триггера и R ≈ S-триггера; Т. задержки (D-триггер), состояние которого и соответствующий ему выходной сигнал повторяют входной сигнал. Кроме Т. этих типов, применяют комбинированные Т., представляющие собой универсальные многофункциональные устройства с большим числом входов.

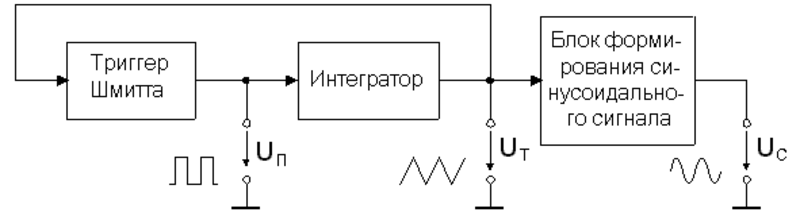

Указанные выше Т. относят к симметричным; применяют также несимметричные Т. (Т. Шмитта). Несимметричный Т. переходит из одного состояния в другое по достижении входным сигналом одного уровня (порога срабатывания), а в исходное состояние возвращается при уменьшении входного сигнала до некоторого др. уровня. Существуют и многостабильные Т., обладающие числом устойчивых состояний, большим, чем два.

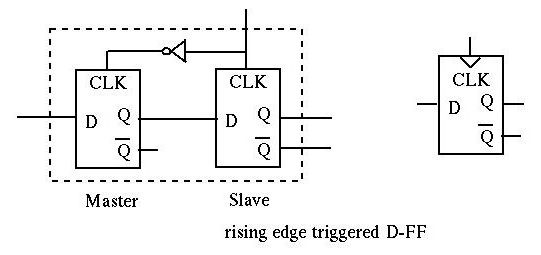

Т. различных типов применяют в устройствах цифровой вычислительной техники и автоматики. С использованием Т. строятся цифровые автоматы с программным управлением для дискретной обработки информации (в частности, счётчики, пересчётные устройства, регистры разных типов, дешифраторы, сумматоры и др.), формирователи импульсов, цифровые делители частоты и т.д. В цифровой автоматике Т. выполняют функции элементарных автоматов с памятью, имеющих 2 состояния, которым соответствуют два возможных значения двоичной логической переменной (х = 0 и х = 1). Такие Т. подразделяются на асинхронные и синхронные. Синхронные (тактируемые) Т. выполняют свои функции только при воздействии на их входы периодических тактовых сигналов (обычно меандрового типа), синхронизирующих работу Т. Синхронные Т. подразделяются на однотактные и двухтактные. Последние представляют собой систему из двух Т., выполняющих одну и ту же логическую операцию, но со сдвигом во времени на длительность полутакта входного тактового сигнала. Удвоение действий Т. необходимо для разделения во времени приёма информации, доставляемой входными сигналами, и передачи информации с выходов Т. на др. элементы устройства (или на его вход).

Лит.: Ицхоки Я. С., Овчинников Н. И., Импульсные и цифровые устройства, М., 1972; Старостин А. Н., Импульсная техника, М., 1973; Каган Б. М., Каневский М. М., Цифровые вычислительные машины и системы, М., 1973.

Ю. Б. Барабанов, И. А. Данильченко,

Е. И. Петровичев.

JK-триггер

Рассмотрим схему простейшего JK-триггера. От RST-триггера он отличается двумя обратными связями, которые устраняют неопределенность в таблице состояний. Назначение входов J и К такое же, как и входов R и S (сброс и установка). Буквы J и К были выбраны в свое время авторами как соседние в алфавите (сравните К и S).

Если входы J, C и К объединить, то получим схему Т-триггера, а если входы элементов ТТЛ DD1.1 и DD1.2 равноправны. Следовательно, как только на объединенный вход С поступит напряжение высокого уровня (после низкого), состояние выходов Q и Q изменится. Вход С можно от общей точки отключить, и в этом случае входная комбинация J = H и К = В переключит триггер: объединенные входы J и К выступят в роли отомкнутого входа С. Таким образом, неопределенности на выходах триггера при обоих высоких входных уровнях в JK-триггере не существует.

Рассмотрим схему управления JK-триггером и его таблицу состояний, в которой две графы: установлено (делается в момент tn) и записано (анализируется состояние выходов после прихода тактового перепада в последующий момент tn+1). При входных сигналах J = H и К = Н состояние выходов не меняется, оно сохраняется таким, каким было в момент установки tn. Напомним, что напряжение низкого уровня на одном входе элемента ТТЛ отменяет прохождение сигналов от других его входов и удерживает выходной сигнал на высоком уровне.

Когда через входы J и К в момент tn загружаем взаимно противоположные уровни, то в последующий момент tn+1 выходы JК-триггера устанавливаются в такие же состояния, как и RS-триггер. Последняя строка таблицы отображает, что при подаче на входы J и К одновременно напряжений высокого уровня (входы можно просто соединить), триггер перебрасывается, переходит в состояние, противоположное предыдущему. Например, если было Qn = B; Qn = Н, то станет Qn+1 = Н и Qn+1 = В

Двухфазный способ управления полным тактовым импульсом С применяется и для двухступенчатых JK-триггеров . Этот триггер, как и простой JK-триггер, имеет обратные связи с выходов на входы, исключающие неопределенное логическое состояние. Схема простейшего двухступенчатого JK-триггера показана на рисунке. Защелка ТМ состоит из элементов DD1.2 и DD1.3. Элементы DD1.1 и DD1.4 — входные ключи с которых снимается сигнал C для управления ТП, защелка RS которого построена на элементах DD1.7 и DD1.8. Сигналы управления подаются на ТП через DD1.5 и DD1.6. Триггер может иметь вход общего сброса данных R, который для этой схемы иногда в литературе называют сlеаr. Многие JK-триггеры имеют также вход предварительной установки S (другое название preset), симметричный входу R, что создает дополнительные входы у элементов DD1,1, DD1.2 и DD1.7.

Рассмотрим осциллограмму переключающего импульса, на которой отмечены этапы работы составного триггера. В момент t1 ТП изолирован от ТМ; в момент t2 разрешается прием данных входами TM. С приходом отрицательного перепада импульса в момент t3 запрещается прием данных входами ТМ, а в момент t4 заканчивается перенос данных из ТМ в ТП. Таким образом, замечательное свойство двухфазного управления состоит в том, что входы приема данных за период тактового импульса, т.е. во время загрузки 1 бита информации, не имеют сквозной связи с выходными цепями. Изоляция входов и выходов обеспечивает устойчивое переключение сложного триггера, если частота тактОвых импульсов нестабильна (дрожит).

Вход

Выход

J

K

C

Q

Q

Н

Н

Н

Н,В

В,Н

В

В

В

В,Н

Н,В

Установлено

Записано

J

K

Qn+1

Qn+1

Н

Н

Без изменений

Qn

Qn

Н

В

Н

В

В

Н

В

Н

В

В

Переброс

Qn

Qn

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

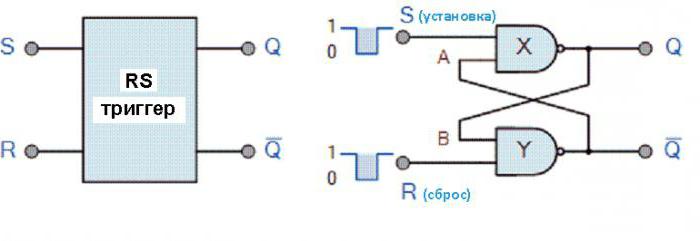

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

Динамические и статические триггеры

Динамические устройства представляют собой систему, одно состояние которой (логическая единица) характеризуется наличием на выходе непрерывающейся последовательности импульсов, имеющих определённую частоту. При втором состоянии (логический ноль) отсутствуют выходные импульсы. Изменение состояний проводится с помощью подачи внешнего импульса. Динамический D-триггер из-за необходимости подачи энергии нашел довольно слабое распространение. Статистическими триггерами называют устройства, каждое состояние которых можно характеризовать неизменным уровнем выходного напряжения (можно в учебной литературе встретить фразу «выходными потенциалами»). Для высокого состояние оно будет близким к напряжению питания, для низкого будет сремиться к нулю. Благодаря такому способу представления выходных данных статистические триггеры часто называют потенциальными. Они делятся на две подгруппы, которые различаются по своему практическому значению для любителей электроники:

- Несимметрические.

- Симметрические.

Своим названием подгруппы обязаны способам организации электрических связей между составляющими элементами схемы. Так, в симметрических триггерах при рассмотрении схемы можно заметить симметрию расположения элементов. В несимметрических устройствах она не наблюдается.

jk триггер

Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов он изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 1.

Таблица 1. Таблица истинности jk триггера.

| С | K | J | Q(t) | Q(t+1) | Пояснения |

| x | x | Режим хранения информации | |||

| x | x | 1 | 1 | ||

| 1 | Режим хранения информации | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы J=1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим записи нуля K=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | 1 | K=J=1 счетный режим триггера | |

| 1 | 1 | 1 | 1 |

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1. Он построен по классической двухтактной схеме. Приведенная на рисунке 1 схема удобна для изучения принципов работы данного триггера в счетном режиме.

Рисунок 1. Внутренняя схема jk триггера

Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы j и k логической единицы одновременно JK-триггер переходит в счетный режим, подобно T триггеру.

Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее временными диаграммами RS- и . Условно-графическое обозначение приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение jk триггера

Цифровые микросхемы обычно собираются на элементах «И-НЕ». Тогда схема, приведенная на рисунке 1, преобразуется в схему, показанную на рисунке 3.

Рисунок 3. jk триггер, собранный на логических элементах «И-НЕ»

В промышленно выпускающихся микросхемах обычно кроме входов j и k реализуются входы R и S, которые позволяют устанавливать jk-триггер в заранее определённое исходное состояние. Именно так реализованы микросхемы 155ТВ1, 133ТВ1, SN7472. На рисунке 4 приведена цоколевка этих микросхем.

Рисунок 4. Цоколевка микросхем К155ТВ1

В названиях отечественных микросхем для обозначения jk триггера присутствуют буквы ТВ. Например, микросхемы К1554ТВ9 и К1554ТВ15 содержат в одном корпусе по два jk триггера. В качестве примеров иностранных микросхем, содержащих jk триггеры можно назвать такие микросхемы, как 74HCT73, 74LVC109 или 74ACT109. В качестве примера на рисунке 5 приведена цоколевка микросхемы К1554ТВ15 (74ACT109)

Рисунок 5. Цоколевка микросхем К1554ТВ15

Так как jk триггер является универсальной схемой, то рассмотрим несколько примеров ее использования. Начнем с примера его использования в качестве обнаружителя коротких импульсов.

Рисунок 6. Схема обнаружения короткого импульса на jk триггере

В данной схеме при поступлении на вход «C» импульса триггер переходит в единичное состояние, которое затем может быть обнаружено последующей схемой (например, микропроцессором). Для того, чтобы привести схему в исходное состояние, необходимо подать на вход R уровень логического нуля.

Теперь рассмотрим пример построения на jk триггере ждущего мультивибратора (схема, формирующая заданную длительность импульса). Один из вариантов схемы ждущего мультивибратора приведен на рисунке 7.

Рисунок 7. Схема ждущего мультивибратора, собранного на jk триггере

Схема ждущего мультивибратора работает подобно схеме обнаружения короткого импульса. Длительность выходного импульса определяется постоянной времени RC цепочки. Диод VD1 предназначен для быстрого восстановления исходного состояния схемы (разряда емкости C). Если быстрое восстановление схемы не требуется, например, когда длительность выходных импульсов гарантированно меньше половины периода следования входных импульсов, то диод VD1 можно исключить из схемы ждущего мультивибратора.

https://youtube.com/watch?v=RRYecDSzxHY

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние

- 1 RS — триггер

- 1.1 Классическая реализация RS-триггера

- 1.2 Временные диаграммы RS-триггера

- 1.3 Другая реализация RS-триггера

- 2 Синхронный RS-триггер

- 3 Синхронный JK-триггер

- 3.1 Схема JK-триггера

- 3.2 Конкретная реализация синхронного JK-триггера

- 4 D-триггер

- 5 Т-триггер

- 6 Двухступенчатые триггеры

- 6.1 Двухступенчатый синхронный RS-триггер

- 6.2 Двухступенчатый D-триггер

- 6.3 Двухступенчатый JK-триггер

- 7 Универсальные триггеры

- 8 Ступенчатый D-триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

RS-триггер на логических элементах

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

RS триггеры

Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2.

Обозначение RS триггера К555ТР2

Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

Могут ли триггеры причинить вред

Что интересно, такое состояние для человека не опасно, но он может воспринимать его негативно и как угрозу, при чем совершенно этого не осознавая. Обычно триггеры, которые вызывают плохие воспоминания и негативные эмоции, называют травматическими.

Триггеры также могут воздействовать на появление приятных воспоминаний, но в психологии это понятие больше понимается, как вызывающий стрессовые эмоции стимул.

Возможно так происходит из-за того, что у человека в памяти лучше откладываются негативные ситуации. Поэтому малейшее влияние на его воспоминания способны вызвать бурю эмоций, но триггер так или иначе все равно не способен причинить реальный вред.

В этом видео вы узнаете о триггерах для продаж:

Практическое использование

Чаще всего триггер используется для генерации сигнала, длительность которого соответствует продолжительности процесса в системе, которую он контролирует. Он может как непосредственно разрешать его начало и конец, так и передавать другим элементам информацию о том, что процесс запустился. Таким образом достигается контроль системы, далее нужно только позаботиться о разрешении ситуации неопределённости.

Вторая важная функция триггера — синхронизация процессов. Это помогает избавиться от лишних и случайных импульсов, возникающих, например, когда несколько входных сигналов изменились в течение очень короткого промежутка времени. Кроме того, с помощью триггеров можно «пропустить» в систему только полные по длительности импульсы или задержать поступающую информацию.

Реализация триггеров и их применение на практике происходит в различных устройствах для запоминания и хранения памяти. Именно этот элемент представляет собой базовую ячейку ОЗУ, способную хранить 1 бит информации в статическом состоянии. Кроме того, его используют для следующих целей:

- в качестве компонентов для создания микросхем различного назначения;

- как организатор вычислительных систем;

- в регистрах сдвига и хранения;

- для изготовления полупроводниковых систем, например, транзисторов и реле.

Триггер является не только базовым элементом электроники, но и простейшим кибернетическим устройством, способным выполнять свою логическую функцию, одновременно поддерживая обратную связь. Таким образом, он используется для создания множества механизмов, целью или условием работы которых является возможность запоминания, хранения, передачи и преобразования информации. Найти триггер можно в любом приборе, начиная от систем переключения питания и заканчивая элементами цифровой микроэлектроники.

Создание запчастей для компьютеров, мобильных телефонов, роботов, управляющих панелей, транспорта и многих других приборов невозможно без использования триггеров. Применяют их и для изготовления простых схем на основе электромагнитного реле — такие конструкции всё ещё используются благодаря своей простоте и высокой защите от помех, несмотря на высокое потребление энергии.

https://youtube.com/watch?v=_YiQrQoRME0

https://youtube.com/watch?v=mlyPpP7PX34

https://youtube.com/watch?v=rWTw8_Pjsgo

Триггер — это оружие маркетологов

Этот термин очень любим маркетологами, поскольку безотказно служит им, принося прибыль. Изучив, что это такое в плане психологии, специалисты сферы продаж выстраивают целые маркетинговые стратегии, основанные на создание запускающих желание купить механизмов.

Реально хорошо работающие триггеры в маркетинге это:

Видеоролик, от начала до конца переполненный маркетинговыми триггерами:

Противостоять таким уловкам сложно, но возможно. Рекомендации из предыдущего раздела актуальны и здесь. Знайте «врага в лицо», прислушивайтесь к своим ощущениям, чтобы не допускать спонтанных действий.

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна область применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.