2.2 MCU карты (опциональный)

Обычно экономические торговые карты, по сравнению с Fun совета CPLD, Им не хватает какой-то “периферия” приходят во главе, кнопки, дисплеем 7 сегменты, и т.д.. и не должны использовать в качестве микроконтроллера “Генератор стимулов”. Следовательно, необходимо будет подключать внешние устройства с помощью, например, макете, а также найти дополнительную карту с микроконтроллером.

В этой связи отмечу, что CPLD работает на 3.3V, так что это не легко использовать в качестве общей платы MCU Arduino Uno (так как он работает на 5V), но это хорошо, чтобы перейти к картам с 3.3V MCU.

Я рекомендую использовать карту “Maple Mini” который использует ARM Cortex M3 MCU 32 бит в Tipo STM32F103, который он же используется в Fun совета CPLD, и которые могут быть запрограммированы с IDE Arduino. Таким образом, вы можете использовать один и тот же рисунок, заботясь, чтобы делать какие-либо небольшие корректировки в случае соединений должны быть разными:

обычно, un “Maple Mini” Его можно приобрести на известных сайтах со всего 3/4$.

Конечно, вы можете также выбрать любой другой микроконтроллер, как ПИК, при условии, работающий на 3.3V. Очевидно, что в этом случае вы не можете использовать “эскиз” примеров, но вы должны сделать свой собственный.

4.3 USB Порядок подключения Blaster

На данный момент мы готовы к загрузке. Но сначала необходимо подключить USB Blaster программатор в соответствии с процедурой, изложенной в загружаемом руководстве кто.

Меры, которые должны следовать в порядке:

- убедитесь, что цель (карта с CPLD) не приведенный в действие;

- подключите USB Blaster программатор для первого USB ПК (Таким образом, будет подаваться с ПК);

- подключите плоский кабель к JTAG 10 проводники к цель;

- подача цель. Если Fun Board CPLD Это приводит соединительный разъем USB платы к второму порту USB на вашем компьютере.

В следующем видео мы показали все этапы в соответствии с процедурой,:

https://youtube.com/watch?v=86GotviRmQQ

4.1 Редактирование проекта

Открыть ранее сохраненный проект из главного меню Quartus II “файл” -> “Открыть проект…” и выберите файл “test1.qfp”

Обратите внимание, что расширение .QFP используется для файлов проекта Quartus II:

Тогда из главного окна:

Мы создаем новый файл для электросхемы реализовать.

В главном меню выберите Quartus II “файл” -> “новый…“:

а затем “Блок-схема / Схема файла“. Это создаст новый файл .BDF:

Теперь мы должны нарисовать схему того, что мы хотим достичь в CPLD.

Мы будем использовать три счетчика 74393 в качестве перегородок 1:256.

Затем выберите значок “Символ инструмента” на панели инструментов редактора:

и написать 74393 в полевых условиях “название“:

нажимать кнопку “ОК” и мы размещаем три счетчика 74393 в листе, используя левую кнопку мыши:

Затем нажмите кнопку (физическое) “ESC” и мы выбираем иконку “Ортогональные Node Tool” сделать соединение:

и мы завершим все, как показано здесь:

Теперь ключ снова “ESC” и riselezioniamo “Символ инструмента“, затем написать”не” в полевых условиях “название“:

posizioniamo и два НЕ ворота, как показано здесь:

Теперь мы добавим входной контакт (часы) и выходной (светодиодный). Кроме того, мы также добавим дополнительный входной контакт для кнопки Fun Board CPLD, который подключается к сигналу “Очистить” общие для трех 74393.

После нажатия кнопки (физическое) “ESC” мы выбираем “Pin Tool” и вспомогательный отбор “вход“:

и мы posizioniamo два входных порта следующим:

и выходной порт для выбора LED “Pin Tool” а затем “Выход“:

posizioniamo и дверь выхода, как показано здесь:

Теперь для большей ясности мы переименуем ворота ввода / вывода (pin_name1, …3) как показано ниже, двойное нажатие на название, чтобы изменить:

На данный момент, редактирование завершено, и было бы целесообразно, чтобы сохранить его.

JTAG[править]

Для работы с jtag-программатором следует создать группу jtag и добавить в неё пользователя, от имени которого будет запускаться Quartus.

groupadd jtag usermod -a -G jtag ИМЯ_ПОЛЬЗОВАТЕЛЯ

Также следует создать udev-правило для разных моделей программаторов, по которому их файл устройства подключается в нужное место с адекватными правами доступа.

В файл /etc/udev/rules.d/99-altera-usb-blaster.rules следует записать:

# USB-Blaster

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6001", MODE="0660", GROUP="jtag", SYMLINK+="usbblaster/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6002", MODE="0660", GROUP="jtag", SYMLINK+="usbblaster/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6003", MODE="0660", GROUP="jtag", SYMLINK+="usbblaster/%k"

# USB-Blaster II

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6010", MODE="0660", GROUP="jtag", SYMLINK+="usbblaster2/%k"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="09fb", ATTRS{idProduct}=="6810", MODE="0660", GROUP="jtag", SYMLINK+="usbblaster2/%k"

После выполнения всех операций по настройке jtag следует перезапустить udevd командой

service udevd restart

и перелогиниться. Или просто перезапустить компьютер.

Adding files, compilation and upload from Quartus

Adding files

From Quartus > Project > Add/Remove Files in Project… > the Settings window appears.

Click the ”…” button at the right of the File name text input.

Select the file that you can find there:C:\dev\fpga\altera\sys-on-prog-chip\de1_blinker\synthesis\de1_blinker.v

Then click Add on the right.

The de1_blinker.v file is added.

Let’s continue by adding all other files.

Click the ”…” button at the right of the File name text input.

Select all 36 files in the following directory:C:\dev\fpga\altera\sys-on-prog-chip\de1_blinker\synthesis\submodules

They are all added immediately (don’t need here to click Add).

Click OK.

In the Project Navigator click the Files tab.

In the list of files, select de1_blinker/synthesis/de1_blinker.v.

Right click > Set as Top-Level Entity.

Compilations

Let’s start a first compilation.

From Quartus > Processing > Start Compilation.

Normally the compilation ends with no errors (only warnings).

This first compilation was to tell Quartus which pins we would like to use.

Let’s now assign correct pins with correct location.

From Quartus > Assignments > Pin Planner.

At the bottom, in the All Pins area, you should see Node Name but without their Location nor their I/O Bank and VREF Group.

To resolve this, we have to open the DE1_pin_assignments.csv, normally provided by Altera.

Notice that this assignments is only for the DE1 board. For the another board use the specific pin assignments CSV file.

Inside we can see that the CLOCK_50’s location is PIN_L1.

We have to add each location to each node.

So, in the Pin Planner, double-click the Location of clk_clk > select PIN_L1.

Automatically the I/O Bank and the VREF Group are added.

Notice: SW2 to SW7 are not used for this tutorial, so you don’t have to assign them if you don’t want to.

Let’s do the same for other nodes:

- clk_clk → PIN_L1

- led_external_connection_export → PIN_R19

- led_external_connection_export → PIN_R20

- switcher_external_connection_export → PIN_M2

- switcher_external_connection_export → PIN_U11

- switcher_external_connection_export → PIN_U12

- switcher_external_connection_export → PIN_W12

- switcher_external_connection_export → PIN_V12

- switcher_external_connection_export → PIN_M22

- switcher_external_connection_export → PIN_L21

- switcher_external_connection_export → PIN_L22

Once done, let’s recompile the project.

From Quartus > Processing > Start Compilation.

This second compilation is really important, don’t skip it.

Sending the design into the board

At this point, we have to send the file chip1.sof, generated by the second compilation, into the board.

This file can be found there:C:\dev\fpga\sys-on-prog-chip\output_files\chip1.sof.

For that, from Quartus > Tools > Programmer.

Normally you just have to click Start to upload the program into the board.

But if the output_files/chip1.sof is not visible on the right, click Add File… and choose it.

Доработки и исправления[править]

Создать исполнимый скрипт /opt/firefox-env:

#!/bin/sh exec /usr/bin/env --unset=LD_LIBRARY_PATH firefox "$@"

Это исправляет запуск справки. В противном случае, firefox со справкой пытается вместо системных загрузить стандартные бинарные библиотеки из комплекта Quartus, от чего завершается аварийно.

В файле ~/intelFPGA_lite/${ver}/modelsim_ase/bin/vsim на строке 210 добавить ядра Linux современных версий в список архитектур:

Сохранить её в ~/intelFPGA_lite/${ver}/lib_old_compat/.

В lib_old_compat/ создать ссылку:

$ ln -s libfreetype.so.6.10.0 libfreetype.so.6

В папке ~/intelFPGA_lite/${ver}/modelsim_ase/linuxaloem переименовать оригинальный vish в vish.zzzz.

Создать скрипт-подмену vish:

cd ~/intelFPGA_lite/${ver}/modelsim_ase/linuxaloem

mv vish vish.zzzz

touch vish

chmod a+x vish

vim vish

В скрипт-подмену vish записать:

#!/bin/sh LD_LIBRARY_PATH=$MODEL_TECH/../../lib_old_compat/ export LD_LIBRARY_PATH exec -a $MODEL_TECH/vish $MODEL_TECH/vish.zzzz "$@"

Это позволяет подгрузить правильную версию библиотеки libfreetype в нужном месте комплекса программ ModelSim. Передача LD_LIBRARY_PATH всему ModelSim не работает — где-то по пути переменная удаляется.

Возможно, вам также будет интересно

Общая характеристика и особенности кристаллов программируемой логики с архитектурой FPGA нового поколения Новое поколение кристаллов программируемой логики с архитектурой FPGA будет представлено тремя сериями ПЛИС — Artix-7, Kintex-7 и Virtex-7, производимыми по High-K Metal Gate (HKMG) технологии 28 нм. Таким образом, фирма Xilinx существенно обновляет спектр продукции, который традиционно был представлен ею на рынке ПЛИС

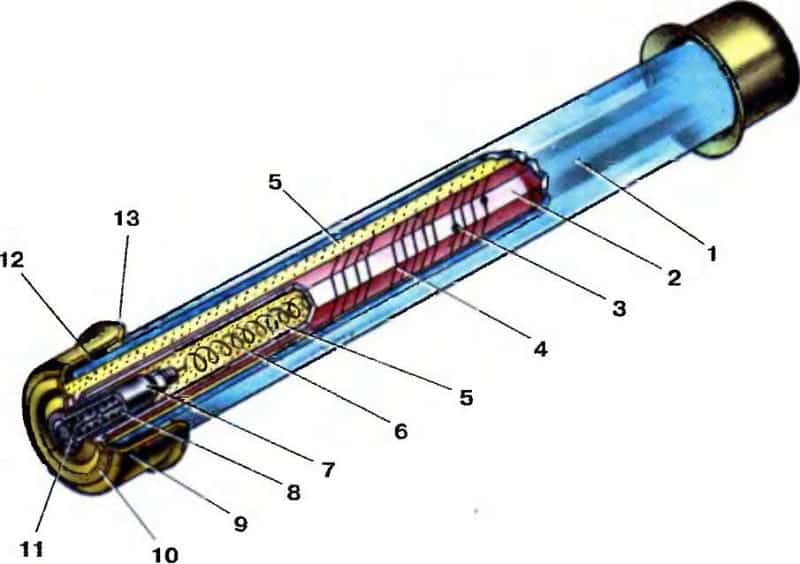

Основные типы магнитопроводов Практически все известные виды вторичных источников питания содержат электромагнитные компоненты, такие как трансформаторы и индуктивности (дроссели, индукторы, реакторы). Обычно эти компоненты имеют одну или несколько обмоток, намотанных поверх магнитопровода из ферромагнитного материала. Использование ферромагнитных материалов позволяет улучшить электрические параметры электромагнитных компонентов, а также уменьшить их размеры и массу. По аналогии с электрическими

Статья посвящена исследованию работы терморезисторов с отрицательным температурным коэффициентом сопротивления, рассмотрению преимуществ и недостатков применения термисторов, принципам построения систем измерения и контроля температуры, а также факторам, влияющим на работу термисторов в качестве датчиков температуры, и снижению погрешности измерительной системы.

2.4 II IDE Quartus

Наконец, вы должны загрузить и установить II IDE Quartus. В дальнейшем я буду использовать версию 13.0.SP1, потому что мне нужно сохранить эту версию для другого проекта с использованием FPGA Cyclone II (Это последняя версия, которая поддерживает эту FPGA). Если вы хотите, вы можете попробовать использовать последнюю версию (в настоящее время 17) который до сих пор поддерживает серию Max II, но вполне возможно, что скриншоты не совпадают ниже используется.

Чтобы скачать версию, вы можете использовать этот 13.0.SP1 ссылка. Е’ Вы должны зарегистрироваться, чтобы перейти к загрузке. Я рекомендую вам выбрать тег “Комбинированные файлы” и скачать около 4.4GB файл все, что нужно.

3. Настройка Quartus II

Как я уже говорил ранее, Все скриншоты относятся к 13.0.SP1 версии IDE.

Кроме того, предлагается конфигурация обозначается Fun Board CPLD, но также рекомендуется для любого другого развития борту используется.

В главном меню выберите Quartus II “файл” -> “Мастер создания нового проекта…“:

то “следующий >“:

и вставить имя папки проекта Вы хотите создать. В этом примере мы будем писать “test1” для всех полей, как скриншоты

Е’ Обратите внимание, что Quartus II Он не любит имена с внутренними пространствами

Тогда мы идем дальше с “следующий >“:

до сих пор “следующий >“:

в настоящее время в “семья” выберите MAX II, в полевых условиях “пакет” выбрать “TQFP” и в области “Доступные устройства” линия “EP240T100C5“.

Тогда мы идем дальше и дальше с “следующий >“:

и снова “следующий >“:

и, наконец, нажмите на “Конец“. Теперь у нас есть пустой шаблон, и вы можете изменить конфигурацию.

В главном меню выберите Quartus II “Назначения” -> “приборы…“:

и нажмите на кнопку “Устройство и параметры контактов…“:

и выберите “Разрешить сброс устройства в масштабе (DEV_CLRn)” е “Включение устройства в ширину вывода позволяют (DEV_OE)“. Это будет включена функцией “DEV_CLRn” е “DEV_OE” CPLD доска Fun Board.

Эти две важные функции: первый сбрасывает триггер всех LE (Логические элементы) с ключом “DEV_CLRn”, а вторая дает возможность, чтобы заставить все контакты ввода / вывода на CPLD в высокий импеданс через переключатель “DEV_OE”.

Теперь мы устанавливаем статус CPLD штифта неиспользуемый. термин неиспользуемый Это означает не указано явно в фазе программирования.

Из этого же окна, выбрать левый “Неиспользованный Pins“:

и выберите в поле “Зарезервировать все неиспользуемые контакты” опция “В качестве входной три- заявил слабым подтягивание“. Это лучшая конфигурация, и многое другое “безопасность” за ла Fun совета CPLD, но рекомендуется также в целом.

Теперь это шанс сохранить проект, который будет использован ниже для первого примера использования, вездесущий мигающий светодиод…

4. Классический проект, чтобы начать: мигающий светодиод

Как была традиция первого примера проекта будет сделать мигающий светодиод.

В дальнейшем я буду продолжать ссылаться на Fun совета CPLD, но содержание, однако, также применимо и к другим вкладкам, имеющим предусмотрительно модифицировать физический штифт по отношению к конфигурации HW карт, используемой.

также, чтобы сделать его еще проще понять, Он будет использовать окружающую среду “схематическая запись” и библиотеки, которые позволяют моделировать поведение HW хорошо известного семейства цифровых интегральных схем 7400. Поэтому он не будет делать какие-либо упоминания об использовании HDL языков, как VHDL, требующий секрет производства специфические.

В этом руководстве будет использоваться в качестве отправной точки проекта test1 ранее сохраненные, собирается реализовать такую конфигурацию, что CPLD, начиная с тактовым входом 36MHz, Он делит его с цепью делителей, чтобы получить частоту примерно 2 Гц. Этот последний будет использоваться для мигания светодиода. Часы 36MHz будет выпускаться с STM32F103 на борту Fun совета CPLD.

В случае использования коммерческой карты, просто выберите соответствующие входной генератор на 50МГц, которые обычно экипирование указанных карт. Частоты будут выпускаться в этом случае примерно на 3 Гц.

About Quartus II

At the time of writing this document, Altera provides Quartus II software in two different versions:

- Quartus II Web Edition — Free version available only for Windows

- Quartus II Subscription Edition — Free 30 day trial. After that period, subscription license is required. Available for Windows and Linux

Although Quartus II Subscription Edition needs a license in order to work, several command line tools that are provided as part of the installation can be used without the need of it. Two important commands of these tools that we will use are jtagd and jtagconfig.

jtagd communicates with and loads compiled designs into Altera devices using JTAG standard in two different connection modes:

-

Local mode — The Altera device is fisically connected to the computer in which jtagd is running

- Remote mode — The Altera device is fisically connected to a remote computer that acts as a server. Quartus II software running on the local computer communicates with the remote Altera device via the remote server

jtagconfig allows us to register and configure connection cables and Altera devices, and setup jtagd to act as a JTAG server

Setting up configuration

The following is a big picture of the steps that will be explained in the following sections:

- Install Quartus II Web Edition in the guest system to be able to create, compile and load designs into Altera devices

-

Set up a JTAG server on host computer

-

Install Quartus II Subscription Edition in the host machine to be able to use jtagd and jtagconfig

-

Use jtagd and jtagconfig to setup a JTAG server

-

-

Communicate the Quartus II Web Edition installed in the guest system with the JTAG server running on the host via virtual networking

- Test configuration by loading a compiled design into Altera device

Редактор содержимого памяти в системном окружении (In System Memory Content Editor)

Анализ данных, записанных в блоки памяти СБИС ПЛ, позволяет упростить отладку систем, в которых содержимое блоков памяти модифицируется в процессе работы (например, проконтролировать содержимое принятого или подготовленного к передаче пакета в системах телекоммуникаций или проанализировать данные, сохраненные в стеке синтезируемого процессорного ядра). Особенно важна возможность анализа содержимого блоков памяти на физической модели, поскольку симулятор пакета Quartus II не позволяет решить эту задачу на имитационной модели.

Доступ к записанным в память данным в процессе работы осуществляется через создаваемый редактором содержимого памяти в системном окружении (InSystem Memory Content Editor) дополнительный порт. Поэтому возможность анализа доступна только для модулей однопортовой памяти RAM: 1 PORT, ROM: 1 PORT, и для параметризируемых модулей констант LPM_CONSTANT. Для анализа в системе содержимого создаваемого блока памяти необходимо указать эту возможность при настройке в редакторе параметризируемых модулей MegaWizard (рис. 12).

Рис. 12. Настройка параметров блока памяти для работы с InSystem Memory Content Editor

Доступ к записанным в настроенную для отладки память данным выполняется с помощью редактора содержимого памяти в системном окружении (рис. 13).

Рис. 13. Окно редактора содержимого памяти в системном окружении

Область настройки JTAG такая же, как и для интерфейса LAI, она позволяет определить положение целевой СБИС ПЛ в JTAGцепочке, выбрать программирующий файл и выполнить конфигурирование. Для сконфигурированной микросхемы становится активной область менеджера тестирования памяти.

Менеджер тестирования отображает доступные для тестирования блоки памяти и константы с именами, данными им при настройке (рис. 12), их статус и характеристики, позволяет выполнять циклическое или однократное чтение, остановку циклического чтения и запись. Считанные из тестируемых блоков памяти значения отображаются в области данных.

Кроме отображения считанных значений область данных позволяет редактировать данные. Для редактирования стандартным образом выделяется и модифицируется код по выбранным адресам. Щелчок правой кнопкой в поле области данных вызывает всплывающее окно редактора, которое облегчает редактирование, позволяет записать модифицированные слова в память, изменять константы (например, при отладке фильтров), экспортировать считанные данные в файл для дальнейшего анализа и импортировать данные из файла для записи в память. В нижнем правом углу окна отображается положение курсора.

Значения в области данных отображаются:

- черным цветом, если считанные данные совпадают c предыдущими отображаемыми данными;

- красным цветом, если считанные данные не совпадают или в СБИС ПЛ записаны новые данные из InSystem Memory Content Editor;

- синим цветом модифицированные, но еще не записанные в блоки памяти СБИС ПЛ данные.

Использование редактора содержимого памяти в системном окружении повышает оперативность отладки и увеличивает ее возможности, так как при этом не требуется переконфигурирования СБИС ПЛ для изменения содержимого блоков встроенного ОЗУ.

Setting up the JTAG server

Setup environment for Quartus II installation script

-

Remove csh and install tcsh on the host system

sudo apt-get remove csh tcsh sudo apt-get install tcsh

-

Make sure that /bin/sh is pointing to bash.

ls -l /bin/sh

lrwxrwxrwx 1 root root 4 2008-11-06 11:53 /bin/sh -> bash

If it is not pointing to bash, delete existing link and create a new one

sudo rm /bin/sh sudo ln -s bash /bin/sh

Install Quartus II Subscription Edition

-

Download Quartus II Subscription Edition Software v8.1 for Linux from Altera’s site

-

Untar 81_quartus_linux.tar in the the host computer, in a directory of your choice

- Go to the directory where you untared the software and execute the installation script

./install

-

Follow the instructions to complete the default installation. If you decide to do a custom installation, read readme.txt or the installation script help

./install --help

-

If you are using USB Blaster to connect the Altera device to the host computer, you will need to enable usbfs, which is disabled by default on Ubuntu 8.04 (Hardy Heron). Follow instructions to do so. If you want to enable USB access to your VirtualBox installation (currently not available for OSE version) follow the instructions as is. Otherwise, change the group vboxusers for a group you’d like to provide the access to usbfs.

Test your installation

Connect and turn on the Altera device to the host computer. Follow the instructions according to the connection cable you are using:

-

USB Blaster — USB cable connection is automatically detected when connected to the host computer, so executing jtagconfig should list the available Altera devices currently connected

$ALTERA_HOME/quartus/bin/jtagconfig

1) USB-Blaster 020B40DD

- LPT cable — (instructions for LPT1 cable missing)

You should now be able to execute jtagd and jtagconfig, that should be found in $ALTERA_HOME/quartus/bin. You will also be able to execute Quartus II IDE with free 30 day trial. In this version, binary compilation and design loading into Altera devices are disabled.

$ALTERA_HOME/quartus/bin/quartus

Create a service for jtagd

jtagd should be run as a service to be able to work as a JTAG server. The correct way to do this is installing jtagd in the system run levels mechanism:

-

Download jtagd init script from here

-

Place the script in /etc/init.d/ directory

-

Create /etc/rcn.d symbolic links

sudo update-rc.d jtagd defaults

The defaults option will create links to start service in 2, 3, 4 and 5 run levels and links to stop service in 0, 1 and 6 run levels

-

Create /etc/jtagd directory

-

Create an empty file called /etc/jtagd/jtagd.conf (needed to store jtagd configuration, which is managed by jtagconfig)

- Create the following symbolic link

sudo ln -s $ALTERA_HOME/quartus/linux/pgm_parts.txt /etc/jtagd/

-

Start jtagd service

sudo invoke-rc.d jtagd

If everything is going ok you’ll be able to connect successfully with your Altera device as

-

Configure jtagd service to act as a JTAG server. A password is required for the server. This password should be used by JTAG clients that want to connect to this server.

sudo $ALTERA_HOME/quartus/bin/jtagconfig --enableremote <password>

If your setup was successful, you should have a jtagd process listening in port 1309

sudo lsof -i :1309

COMMAND PID USER FD TYPE DEVICE SIZE NODE NAME jtagd 5568 root 4u IPv4 14518 TCP *:1309 (LISTEN)

Explanation

For this tutorial, we will realize a system which lights two LEDs from two switchers.

We will use the Altera DE1 board and Quartus II 13.0sp1.

If you had the DE2, you would have only few things to change. So keep reading.

It’s not so easy to all understand first time, but at the end you will be proud to achieve this really interesting tutorial.

This project is a mix between hardware and software.

We’re indeed going to choose which parts of hardware we want, realize the design and then create a software library from this design. Then we will be able to create a program in C language in order to upload this program into the DE1 board.

For that, the design hardware will be created with Qsys and a file will be generated, that’s de1_blinker.sopcinfo.

With this file we will be able to create the BSP (Board Support Package) that it will be compiled with our user application in C language.

The user application and the BSP will be created with SBT (Software Build Tools).

These tools are composed of:

- GCC

- A special Nios II GNU library C

- A HAL (Hardware Abstraction Layer)

SBT is a tool based on Eclipse, a well known open source IDE.

You don’t need to have Eclipse already installed because the Indigo version will be launched for you when you will decide to create your BSP.

Indeed a hidden Eclipse was installed with your Quartus installation.

After the compilation and the linkage of the user application and the BSP, a new file will be added: de1_blinker.elf.

At this point, we will send it to the board in order to program it.

Finally we will see the result directly on the board with red LEDs lit from switchers.

4.2 Назначение физического штифта

Теперь вам нужно связать входные / выходные порты различного физического штифта CPLD. Но прежде чем предшествуют следует использовать маленькую хитрость, чтобы сделать следующий шаг легче. На самом деле, однако, мы должны теперь сделать сборник весь проект, таким образом, они будут автоматически доступны на Pin Planner имена портов, которые мы использовали в редактор схем в предыдущем шаге. Имея дело с устройствами 100 а штифт не является тривиальным…

В связи с этим, мы нажимаем на иконку “компиляция“:

и мы ждем завершения компиляции:

Если мы все сделали правильно, Они не должны появляться ошибки, но любой предупреждение что игнорировать.

Теперь нажмите на кнопку “ОК” и нажмите на иконку из “Pin Planner“:

окно будет активирован Pin Planner:

Это место, чтобы связать физические контакты к двери электрической схемы, и которые определяют электрические параметры (логические уровни, eventuali подтягивающий, и т.д ..).

Теперь мы начинаем ассоциировать с физическим штифтом с помощью поля “Место нахождения” в нижней части окна:

Для того, чтобы присвоить физический штырь должен нажать пересечение линии затвора, чтобы быть связан с колонной Место нахождения. В случае Fun совета CPLD от электрической схемы показывает, что входной контакт часов (даль контактный 29 MCO из STM32F103) Он соединен с контактом 14 CPLD, Аналогично светодиод LED1 соединен с контактом 50 и ключ USR4 соединен с контактом 54 CPLD.

Если вы используете другую карту вам нужно будет внести необходимые изменения.

Вы закончите:

Теперь вам нужно внести некоторые коррективы в некоторые параметры по умолчанию некоторых физических контактов, которые принимают во внимание HW из CPLD совета Fun Board. Во-первых в случае активации внутреннего сопротивления штифтовой подтягивание 14 (Часы) поскольку в определенных условиях выход STM32 MCO в высоком импедансе

Это может предотвратить состояния “плавающий“

Во-первых в случае активации внутреннего сопротивления штифтовой подтягивание 14 (Часы) поскольку в определенных условиях выход STM32 MCO в высоком импедансе. Это может предотвратить состояния “плавающий“.

Для этого мы выбираем “На” по столбцам “Слабые нагрузочный резистор” (Примечание: ли в вашей системе не появляются определенные столбцы, идти с мышью на любом заголовке столбца и нажмите правую кнопку. На этом этапе выбранный столбец должен быть добавлен к текущему представлению):

Затем необходимо принять во внимание, что кнопка USR4 подключена к аналоговой схеме для де-подпрыгивая, Следовательно, он должен быть активирован один триггер Шмитта вход штифта 54:

мы можем закрыть окно в этой точке Pin Planner (Вам не нужно, чтобы сохранить что-либо в явном виде). Теперь вам нужно сделать новую компиляцию проекта, как и раньше:

и это хорошая практика, чтобы проверить, что все контакты назначены после компиляции правильны. Для этого кликаем на папку “монтер“:

то папка “выбор ресурсов“:

а затем выберите пункт “Все штыри пакета“:

Теперь вы можете проверить, что все контакты соответствуют ожидаемым.

4.6 Эскиз для генерации тактового сигнала на 36MHz

Ранее мы говорили, что необходимо для создания часов, чтобы дать вклад в CPLD. Для этого мы будем использовать MCU STM32F103 на борту Fun совета CPLD.

В случае использования на другую вкладку, вы должны сделать для того, чтобы принести / генерировать тактовый сигнал на CPLD.

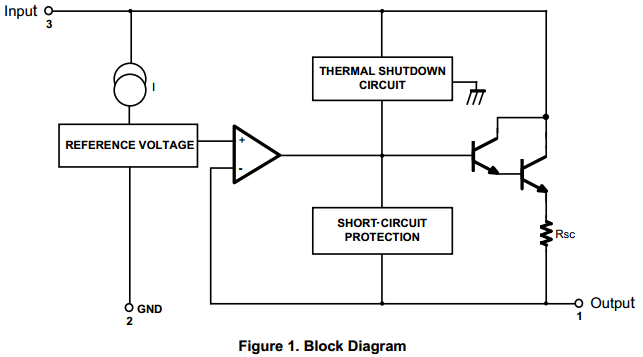

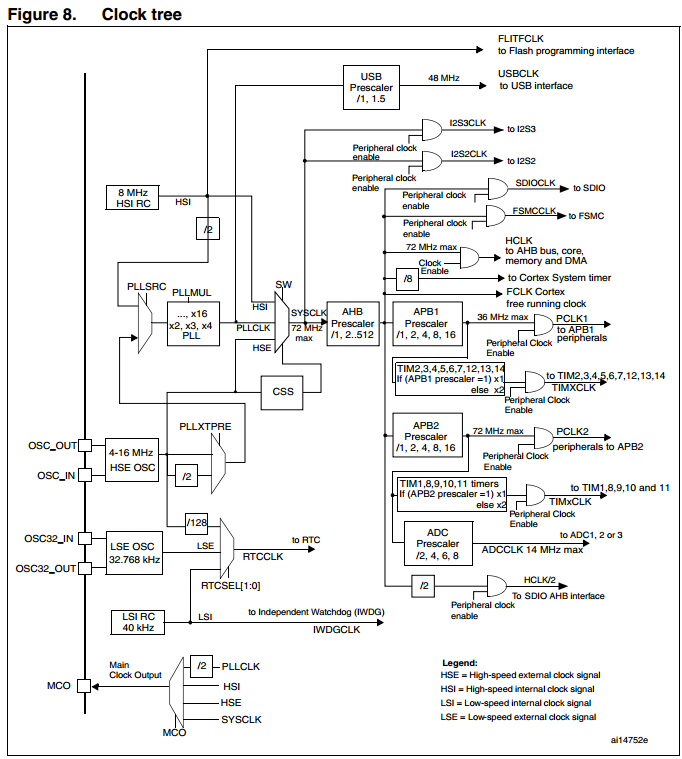

Схема блоков синхронизации STM32F103

Эскиз, который активирует штифт МКО выглядит следующим образом:

недействительные установки() {

// поместить ваш код установки здесь, один раз запустить:

// Установите штифт MCO для вывода часы на CPLD (GCLK1 контактный 14). См STM32F103 Справочное руководство RM0008

RCC_BASE->CFGR = RCC_BASE->CFGR | 0x07000000; // Набор МСО знак равно 111 (внутри регистра RCC_CFGR) для вывода часы 36MHz

GPIOA->regs->CRH = GPIOA->regs->CRH | 0x00000003; // Установить режим вывода на PA8 @ Max Freq 50МГц (MODE8 знак равно 11)

GPIOA->regs->CRH = GPIOA->regs->CRH & 0xFFFFFFF3; // Установить режим вывода на PA8 как общий выход двухтактного (cnf8 знак равно 00)

GPIOA->regs->CRH = GPIOA->regs->CRH | 0x00000008; // Установить режим вывода на PA8 в качестве альтернативного выхода двухтактного (cnf8 знак равно 10)

}

недействительный цикл() {

// положить основной код здесь, запускать несколько раз:

}

Конечный результат показан в следующем видео :

https://youtube.com/watch?v=3HywMqIvg4A

Обратите внимание, что при нажатии на кнопку сброса (сброс MCU) индикатор перестает мигать на некоторое время, так, во время сброса и последующая перезагрузка перестает тактовый сигнал, пока загрузчик не передает управление программе пользователя, который активирует. Вы также можете увидеть эффект кнопки DEV_CLRn что сбрасывает все шлепанцы внутри CPLD, решений на сброс счетчиков, сконфигурированных в том же CPLD

При нажатии кнопки USR4 счетчики сигнальных выключателей Очистить, получения того же эффекта

Вы также можете увидеть эффект кнопки DEV_CLRn что сбрасывает все шлепанцы внутри CPLD, решений на сброс счетчиков, сконфигурированных в том же CPLD. При нажатии кнопки USR4 счетчики сигнальных выключателей Очистить, получения того же эффекта.

Активация переключателя DEV_OE вынуждены в высокий импеданс через штифт ввода / вывода из CPLD, с последующим прерыванием фартука.

5. Ссылки на углубление

- Руководство Quartus II V13.1 кто;

- Руководство устройства Макс II кто;

- Технический паспорт MCU STM32F103 кто;

- Справочное руководство RM0008 (MCU STM32F103) кто;

| ГОЛОСОВАНИЕ |

Итог[править]

- Quartus запускается из командной строки по прямому пути ~/intelFPGA_lite/${ver}/quartus/bin/quartus.

- Quartus Programmer — ~/intelFPGA_lite/${ver}/quartus/bin/quartus_pgmw

- ModelSim — ~/intelFPGA_lite/${ver}/modelsim_ase/bin/vsim

Для диагностики проблем подключения программатора можно запустить jtag демон в отладочном режиме:

jtagd --foreground --debug

Перед этим следует убить работающую копию сервера, запускаемую автоматическими любым инструментом, использующим jtag (напр. Programmer и SignalTap).

Добавление ярлыков на рабочий стол оставим на усмотрение читателя =)