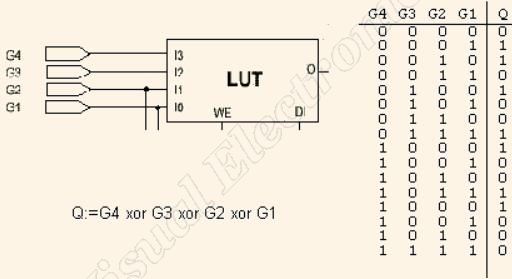

Логическая таблица.

Роль основного логического элемента в ПЛИС играет логическая таблица (ЛТ) или look-up table (LUT), представляющая собой однобитное ОЗУ на 16 ячеек. В ЛТ по адресу G3,G2,G1,G0 записана единица, если код адреса представляет собой конституенту единицы заданной четырехвходовой логической функции. Например, если по адресу 1,1,1,1 записана единица, а по остальным адресам — ноль, то ЛТ реализует четырехвходовую функцию И. На рис. показан пример кодирования функции Исключающее ИЛИ на четыре входа.

Триггеры ЛТ входят в состав программирующего сдвигового регистра и их начальное состояние заполняется в период конфигурирования ПЛИС.

Содержимое пакетов уровня транзакций

Рисунок 3 — Пример запроса на запись в память длиной в 1 DWРисунок 4 — Пример запроса на чтение из памяти длиной в 1 DWРисунок 5 — Пример успешного ответа на чтениеРисунок 6— Пример ответа о неподдерживаемом запросеРисунок 7 — Пример заголовка запроса на запись 128 байтТаблица 4 — Перечень сокращений для полей заголовков

| № п. | Обозначение поля | Название поля | Назначение |

|---|---|---|---|

| 1 | TC | Категория трафика ‒ Traffic Class | Определяет принадлежность к виртуальному каналу |

| 2 | Атр. | Атрибуты | Устанавливают порядок очередности пакетов: строгий, нестрогий, очередность только по ID, нестрогая очередность вместе с адресацией по ID. |

| 3 | TH | Наличие подсказки обработки пакетов ‒ TLP Processing Hint | Показывает, есть ли подсказка по обработке пакета в битах двойного слова с младшими байтами адреса. |

| 4 | TD | Наличие на уровне транзакций контрольной суммы пакета ‒ TLP Digest | Показывает, является последнее двойное слово в пакете контрольной суммой или нет. |

| 5 | EP | Наличие ошибки целостности данных пакета | Показывает, нарушена целостность данных пакета или нет. |

| 6 | AT | Трансляция адреса ‒ Address Translation | Определяет, должен ли адрес быть транслирован: адрес не транслирован, запрос трансляции, адрес транслирован |

| 7 | BE | Активные байты в первом и последнем двойных словах ‒ Byte Enable | Определяет положение активных байт внутри первого и последнего двойных слов |

| 8 | PH | Подсказка по обработке пакета ‒ Processing Hint | Подсказывает получателю пакета, как должен использоваться пакет, а также ‒ структуру данных |

| 9 | BCM | Наличие изменения числа байт | Показывает, было ли изменено количество байт в пакете. Флаг может устанавливать только отправитель в лице PCI-X устройства |

- унаследованные прерывания (Legacy Interrupts или INT);

- прерывания в виде сообщений (Message Signaled Interrupts или MSI);

- расширенные прерывания в виде сообщения (Message Signaled Interrupts Extended или MSI-X).

Рисунок 8 — Таблица векторов прерываний MSI-XРисунок 9 — Таблица флагов ожидающих прерываний

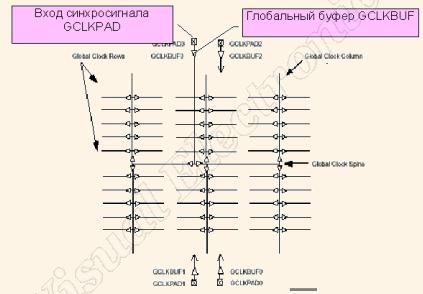

Система синхронизации.

Одним из принципов разработки проектов для ПЛИС является принцип однотактной синхронизации, согласно которому все триггеры в блоке срабатывают одновременно по одному сигналу синхросерии. Для его реализации в ПЛИС синхросигналы распространяются по быстродействующей древоообразной сети, которая обеспечивает почти одновременный приход фронта синхроимпульса на синхровходы всех триггеров.

Для надежного функционирования ПЛИС синхросигнал должен подаваться через вывод GCLKPAD и попадать в сеть синхросерии через буфер GCLKBUF. В ПЛИС предусмотрено 4 вывода GCLKPAD, размещенных на противоположных сторонах ее корпуса. Синхросигнал может вырабатываться и внутри ПЛИС, но в этом случае его следует завести в сеть синхросерии через глобальный буфер BUFG.

С помощью спроектированного синхронного автомата, сконфигурированного в ПЛИС, можно изменять частоту и фазу синхросерии. Но в этом случае ее временные параметры будут недостаточно стабильными и поэтому такой подход обычно не применяется. Для надежного регулирования частоты синхросерии в ПЛИС включают делители частоты синхросерии с автоподстройкой — блоки CLKDLL. На рис. показана типичная схема его включения. Блок CLKDLL обеспечивает умножение частоты синхросерии в 2 раза, сдвиг ее фазы на 90, 180 и 270 градусов, деление на 1.5, 2, 2.5, 3, 4.5, 8 и 16.

Шины с тремя состояниями.

Применение шин с тремя состояниями — типичное схемное решение вычислительных устройств, реализованных на плате. Благодаря такому решению, легко достигается многомодульность и наращиваемость системы, низкие аппаратурные затраты и малые задержки в системе межсоединений. Внутри заказных СБИС редко применяются шины с тремя состояниями из-за технологических трудностей их безотказной реализации, а также увеличенной задержки на их переключение.

Несмотря на это, в ПЛИС фирмы Xilinx всё-таки широко применяются шины с тремя состояниями, хотя это существенно повышает их себестоимость. Зато, во-первых, проще выполнить переход от проекта схемы на плате к проекту системы на кристалле. Во-вторых, ВУ с общими шинами, к которым подключено несколько десятков модулей, имеет аппаратные затраты в несколько раз меньше, чем такое же ВУ, в котором шины заменены на эквивалентную схему из системы мультиплексоров. В-третьих, с помощью общих шин можно эффективно реализовать встроенное распределенное ОЗУ, о котором пойдет речь ниже.

Для реализации общей шины каждый КЛБ имеет два буфера с тремя состояниями BUFT , которые через транзисторы-перемычки могут подключаться к общим шинам, проходящим вдоль всего кристалла. В обычных шинах третье состояние характеризуется уровнем, находящимся между уровнями логической 1 и логического 0. Но если такую шину реализовать внутри микросхемы, то в случае, когда все тристабильные буферы будут в третьем (закрытом) состоянии, их выходные транзисторы будут полуоткрытыми и могут выйти из строя. Для исключения такого электрического режима в ПЛИС общая шина нагружена на концах специальной триггерной схемой — Weak Keeper , которая выводит уровень шины или к уровню H, или к уровню L (слабые 1 или 0), если все буферы закрыты.

Неправильное функционирование общей шины, когда несколько источников с разными уровнями подключаются к шине, может вывести ПЛИС из строя. САПР ПЛИС тщательно проверяет, чтобы спроектированная общая шина функционировала правильно. Поэтому не рекомендуется ручное редактирование файла прошивки, так как случайная ошибка в коде может привести к неправильной работе общей шины и порче ПЛИС.

Что собой представляет плисовая ткань

Само слово «плис» пришло к нам из шведского языка, хотя, с французского это слово переводится как «плюш». Что же представляет собой эта ткань? Как правило, ее основу составляет хлопчатобумажное полотно, хотя изредка используют и шерсть. Сходство с бархатом создается благодаря короткостриженому ворсу. Правда, длина ворса все равно больше, чем у бархата. Следовательно, все виды плиса относятся к уточно-ворсовым (ткань состоит из утка, основы и стриженого ворса). Сам процесс создания ткани заключается в переплетении хлопчатобумажной основы с утком, который образует петли. Чтобы петли стали ворсом, их стригут и прочесывают.

Для создания основы применяется полотняное или саржевое плетение. Плюс такой технологии в том, что петли ворса будут очень прочно держаться в плетении и не начнут сыпаться даже после многократных стирок. Но это же плетение очень затрудняет пошив плисовых изделий. Поэтому мелкие и сложные детали из плиса обычно не делают. Ну и, конечно, сам ворс является прекрасным пылесборником, как любая подобная ткань.

Что такое плис и с чем его носить

«Дешевый бархат», «бумажный бархат» — как только не называли плис за века его использования. Ткань приобрела популярность еще в семнадцатом веке, когда мелкое дворянство и зажиточные крестьяне начали шить из него одежду. Именно такая целевая аудитория поясняется доступной стоимостью плиса и его схожестью с дорогостоящим бархатом. Следовательно, его выбирали любители шика, которые не могли позволить себе натуральный бархат. В России эта ткань появилась веком позже, а изначально плис производили только в Европе. Упоминание о плисовой ткани можно найти даже в литературных произведениях российских классиков: в пушкинской «Барышне-крестьянке» упоминается плисовая куртка, а в гоголевских «Мертвых душах» у знатной дамы была обувь из плиса. В определенных сферах плис не теряет популярности и в наши дни.

История создания и описание плиса

Название этой ткани произошло от латинского слова «pilus», что переводится как «волос». Впервые материал стали изготавливать в XVII веке. Широкое распространение он получил спустя два столетия, после того, как в Манчестере открылись фабрики по производству плиса. В те времена материя стоила недорого, поэтому была доступна всем слоям населения.

На территории России ткань появилась в XVIII веке и сразу стала очень популярной среди всех сословий. Дворяне и зажиточные люди носили плисовую домашнюю одежду и комфортную обувь.

Материал обладает высоким ворсом и характерной рубчатой структурой. Плис прочный и имеет красивый внешний вид.

Это интересно: Лиоцелл: что это за материал? Ткань из волокон эвкалипта — отзывы об изделиях

Продукция Actel на российском рынке

Если до недавнего времени продукция корпорации Actel поступала в Россию по полуофициальным каналам и продавалась без всяких гарантий, то теперь ситуация коренным образом изменилась. Уже в течение двух лет успешно функционирует официальное представительство фирмы Actel в России и на Украине, осуществляющее поставку всех типов ПЛИС, сопутствующее оборудование и программное обеспечение, а также техническую поддержку пользователей

Еще одной важной функцией представительства является оформление лицензионных документов на ПЛИС для космического и военного применения, поскольку импорт этой продукции требует разрешения со стороны государственных структур США

Технологический процесс

Микроконтроллер содержит одно или несколько процессорных ядер (CPU) вместе с ОЗУ, а также флэш-память, содержащую программную память, которая также называется машинным кодом (. hex-файл), каждый машинный код представляет собой инструкцию, выполняемую на процессоре.

Однако, программирование ПЛИС зависит от технологии памяти. Существуют различные технологии построения ПЛИС, например на основе SRAM или флэш-памяти и однократно программируемые ПЛИС. Ячейка памяти хранит конфигурацию ПЛИС, которая написана на языках RTL, и с помощью среды разработки преобразуется код в файл .bit, который используется для конфигурирования ПЛИС.

Загрузка файла конфигурации в микросхему ПЛИС

В первую очередь стоит разобраться с режимом загрузки ПЛИС. Для тех, кто только начинает знакомится с темой, проведу маленький экскурс. Хотя на моей плате установлена ПЛИС Altera (Intel) семейства Cyclone IV E, методы загрузки аналогичны для всей группы ПЛИС Cyclone, и есть подозрение, что в том или ином виде подходят для многих других семейств.

В ПЛИС данного типа используется энергозависимая SRAM для хранения конфигурационных данных. Эти конфигурационные данные определяют функционал итогового устройства. На профессиональном жаргоне эти данные часто называют «прошивкой». Таким образом, прошивка хранится в специальном ОЗУ и каждый раз при включении устройства должна быть загружена в кристалл ПЛИС. Существует несколько способов (схем конфигурации), которыми прошивка может быть загружена в SRAM (список актуален для Cyclone IV E):

- Активный последовательный (Active serial (AS)).

- Активный параллельный (Active parallel (AP)).

- Пассивный последовательный (Passive serial (PS)).

- Быстрый пассивный параллельный (Fast passive parallel (FPP)).

- JTAG.

Выбор конкретного режима загрузки выполняется с помощью внешних выводов ПЛИС (группа MSEL). Режим JTAG доступен всегда. Активный режим подразумевает, что при подаче питания ПЛИС самостоятельно вычитывает данные из внешней памяти (последовательной или параллельной). В пассивном режиме ПЛИС ждет, когда внешний носитель в инициативном порядке передаст ей данные конфигурации. Данные схемы хорошо укладываются в концепцию ведущий (Master) — ведомый (Slave). В активных режимах ПЛИС выступает в качестве ведущего, а в пассивных — в качестве ведомого.

В рассматриваемой задаче не ПЛИС, а пользователь должен решать, когда должна обновляться прошивка, поэтому режим загрузки должен быть пассивным. А для экономия ножек микросхемы выбираем последовательный интерфейс. Здесь подходит пассивный последовательный (PS) режим и JTAG. Логика работы JTAG несколько сложнее, поэтому остановимся на первом варианте.

Ниже на рисунке показана схема подключения ПЛИС к внешнему контроллеру для загрузки в режиме PS.

Для начала конфигурации внешний ведущий контроллер должен генерировать переход из низкого уровня в высокий на линии nCONFIG. Как только ПЛИС будет готова к приему данных, она сформирует высокий уровень на линии nSTATUS. После чего ведущий может начать передавать данные по линии DATA, а соответствующие тактовые импульсы — по линии DCLK. Данные должны передаваться в целевое устройство до тех пор, пока на линии CONF_DONE не установится высокий уровень (или данные не закончатся), при этом ПЛИС перейдет в состояние инициализации. Следует учесть, что после того как CONF_DONE установилась в единицу, нужно подать еще два тактовых импульса, чтобы началась инициализация ПЛИС.

Данные передаются младшим значащим разрядом (LSB) вперед, то есть, если конфигурационный файл содержит последовательность 02 1B EE 01 FA (пример взять как есть из Handbook), на линии данных должна быть сформирована последовательность:

Таким образом, используется всего пять линий: линии DATA и DCLK — для последовательной передачи, линии nCONFIG, nSTATUS, CONF_DONE — для управления.

По своей сути режим PS есть не что иное, как SPI с дополнительной манипуляцией флагами.

Скорость передачи данных должна быть ниже указанной в документации максимальной частоты, для используемой в проекте серии Cyclone IV E — это 66 МГц.

Минимальной же частоты передачи не существует, теоретически можно приостановить конфигурацию на неопределенное время. Это дает отличные возможности пошаговой отладки с участием осциллографа, чем мы непременно воспользуемся.

На рисунке ниже показана временная диаграмма интерфейса с наиболее значащими таймингами.

Экономическая целесообразность и тенденции развития

Поскольку фирма Actel изначально разрабатывала свою продукцию для аэрокосмического рынка, вопросы цены на ее ПЛИС являлись для потребителей вторичными, уступая вопросам надежности и радиационной стойкости. В самом деле, цена даже самой дорогостоящей радиационно-стойкой ПЛИС вместе с программатором много меньше стоимости разработки и изготовления заказной ПЛИС аналогичной функциональности. Однако с появлением ПЛИС, выполненных по технологии Flash, фирма сделала уверенный шаг на рынок коммерческих и промышленных устройств, предложив вполне конкурентные цены на свою продукцию. Следует подчеркнуть возможность получения вторичной выгоды за счет исключения ненужных при применении ПЛИС Actel устройств, таких как загрузочное ПЗУ, мониторы питания, мощные фильтры и т. д.

Для крупносерийного производства электронных изделий представляют интерес коммерческие ПЛИС, выполненные по Antifuse-технологии, благодаря своей невысокой цене, низкому энергопотреблению и надежности.

В качестве тенденций развития продукции корпорации Actel на ближайшее будущее следует выделить предстоящий выпуск на рынок серий ProASIC3/3E по очень привлекательным ценам (инженерные образцы уже распространяются). В чуть более далекой перспективе следует ожидать появление ПЛИС, выполненных по недавно анонсированной технологии Fusion, совмещающих на одном кристалле как цифровую, так и аналоговую части.

Особенности создания бинарного файла конфигурации под микросхему(ы) памяти при работе с ПЛИС от Intel Altera или Воронежского Завода Полупроводниковых Приборов для последующего преобразования в файл формата .pof

Как ранее упоминалось, необходимо учитывать размер данных конфигурации для конкретной ПЛИС, и на основе этого подключать каскадным образом нужное количество микросхем памяти. Более наглядно для микросхем ПЛИС семейства Cyclone информация представлена на рисунке 3.

Размер данных, необходимый для конфигурации других микросхем ПЛИС, должен быть представлен в официальной документации.

Для загрузки ППЗУ 5576РС1У используются файлы с расширением .pof, которые программируются с помощью Quartus II посредством USB Blaster. Но не для всех семейств ПЛИС поддерживается создание pof-файлов для 5576РС1У из Quartus II. Для решения этой проблемы применяется набор программ, которые преобразуют файл(ы) формата .rbf (простой бинарный файл с ПО), в файл(ы) необходимого расширения .pof. Архив со всеми поставляемыми программами находится в подразделе «Файлы для скачивания» после статьи — архив PROM_CREATOR.zip.

Свойства плиса и правила ухода

Изначально плис выпускали только однотонным, для одежды, обуви. Позднее, из плиса начали изготавливать шикарные гобелены, которые можно назвать настоящим произведением искусства. Сегодня узорчатый плис чаще всего используется для отделки мебели.

Для пошива изделий из плисовой ткани практически нет никаких особенных правил (за исключением вельвета, в котором следует избегать швов, повторяющих полосы на самой ткани). Самое главное, это тщательно и аккуратно отделать края, чтобы впоследствии они не начали рассыпаться.

Сейчас плис производят на многих ткацких фабриках в России и по всей Европе. Качество ткани из разных регионов мало отличается, поэтому особого значения фирма-производитель не имеет.

Одно из самых главных преимуществ – устойчивость к складкам. Да-да, плис практически не мнется, гладить его не нужно. Этот нюанс особенно важен для одежды из плиса, уход за которой не доставит вам особенных хлопот. Но не стоит забывать, что плис довольно чувствителен к стирке. Как уже было сказано, ворсинки он не теряет, однако, после контакта с водой ворс «склоняется» к основе. То есть, ткань выглядит «прилизанной». Этот эффект можно устранить только прочесав ткань мягкой щеточкой или отпарив ее.

Советы по уходу за изделиями

В зависимости от состава плисовой ткани советы по уходу могут разниться, однако базовые советы связаны с наличием ворса и являются следующими:

- машинная стирка не рекомендуется;

- ручная стирка разрешена только для тканей на основе синтетики. При этом не допустимы выкручивающие движения, трение и сильное влияние механики;

- сушка разрешена исключительно в природных условиях;

- гладить лучше на режиме отпаривания, в совершенстве – воспользоваться отпаривателем;

- при надобности глажки при помощи утюга необходимо не забывать, что гладить можно лищь с обратной стороны, на подложке из мягкого ворсистого материала;

- природный материал стирать нельзя, только сухая химчистка;

- можно очистить изделие от пыли сухой щеточкой или при помощи пылесоса, установив его на небольшую мощность.

Не обращая внимания на много заменителей, плис до сих пор, как и 2 столетия назад, считается достаточно распространенным материалом, особенно в производстве мебели.

Создание файлов .pof из бинарных файлов .rbf (Altera и Воронежский Завод Полупроводниковых приборов) и .bin (Xilinx) для последующего программирования в подпрограмме «Programmer» САПР Quartus II средствами USB Blaster

Для создания файлов .pof требуется несколько программ, которые поставляются официально и доступны для загрузки в подразделе «Файлы для скачивания» после статьи — архив PROM_CREATOR.zip. Каждая программа имеет входные параметры в виде файла определенного формата и выходные параметры в виде файла нужного выходного формата.

Первая программа из этой группы «rbf2svf.exe», которая конвертирует полученный на этапе компиляции бинарный файл в формат .svf.

Синтаксис этой программы следующий:rbf2svf.exe <входной файл> <выходной файл>

Соответственно,

- для одной ППЗУ: rbf2svf.exe test.rbf test.svf

- для двух ППЗУ: rbf2svf.exe test.rbf test.svf /2

/2 test1.svftest2.svftest.svf.svf«svf2pof.exe»Altera«convert_epc_file.exe»

svf2pof.exe <входной файл> <выходной файл>

Соответственно,

- для одной ППЗУ: svf2pof.exe test.svf test.pof

- для двух ППЗУ: svf2pof.exe test1.svf test1.pof и svf2pof.exe test2.svf test2.pof

.batrbf2pof.batrbf2pof_v2.bat

- rbf2pof.bat <входной файл> <выходной файл> — создание одного образа;

- rbf2pof_v2.bat <входной файл> <выходной файл> — создание двух образов.

Обратите внимание, что данные программы работают не только с бинарными файлами формата .rbf, но и с бинарными файлами формата .bin

После полученных файлов .pof можно приступать к их загрузке в соответствующие ППЗУ с помощью САПР Quartus II, подпрограмма «Programmer» средствами USB Blaster.

Но прежде чем к этому приступить, следует отметить одну особенность при работе с бинарными файлами, которая может иметь частный характер в зависимости от размера полученного бинарного файла и количества микросхем памяти в цепочке. Желательно, чтобы количество байт, размещаемое в каждое ППЗУ в цепочке, было чётным. Соответственно, при разбиении исходного бинарного файла на необходимое количество ППЗУ это условие должно удовлетворяться. Если бинарный файл не удовлетворяет таким условиям, то необходимо его дополнить значения «FF» в конце файла, открыв бинарный файл блокнотом.

Например, полученный .bin файл для Spartan 3 содержит 402.936 байт или 3.223.488 бит, при разбиении его на два ППЗУ получается по чётному количеству байт 201.468. Поэтому перед созданием .pof файла .bin не требует правки. Файл, полученный для Spartan 6, содержит 801.462 байт или 6.411.696 бит, поэтому при разбиении его на два ППЗУ получается 400.731 байт. Следовательно, перед созданием .pof необходимо дополнить .bin файл двумя байтами «FF», чтобы при разбиении его на два ППЗУ получалось 400.732 байта.

Если же требуется каскадное включение более двух микросхем ППЗУ, то следует учитывать следующие особенности работы программы «rbf2svf.exe». Разбиение на файлы ориентировано на чётное количество байт в бинарном файле (при разбиении на соответствующее количество ППЗУ) и на чётное количество ППЗУ в цепочке. Если требуется загрузка нечётного количества байт или количество ППЗУ в цепочке нечётное, то требуется доработка «rbf2svf.exe» под конкретное приложение. Для решения этой задачи в архиве PROM_CREATOR.zip приложены исходные коды этой программы.

Возможно, вам также будет интересно

Программируемые устройства Xilinx С 1984 года, когда впервые в мире Xilinx выпустила программируемые логические интегральные схемы (ПЛИС) с архитектурой FPGA (Field Programmable Gate Array), и по настоящее время компания является ведущим мировым производителем микросхем программируемой логики. Технологии Xilinx предоставляют возможность производителям электронного оборудования минимизировать риски за счет сокращения времени на разработку новой продукции и сроков

С момента своего появления программируемые логические устройства (PLD) начали постепенно вытеснять дискретно-логические интегральные схемы. Дальнейшее развитие PLD до сложных PLD (CPLD) ускорило данную тенденцию, а последние разработки доступных, быстрых, больших матричных кристаллов с возможностью перепрограммирования (ПЛИС) почти завершили этот процесс. Как удалось создать полноценный логический анализатор в таком компактном корпусе? PLD и CPLD устройства могут

В последние годы в технологии создания термоэлектрических микромодулей достигнут значительный прогресс. Причем одновременно с прогрессом в так называемой объемной технологии получила развитие и новая методика изготовления термоэлектрических модулей, вобравшая известные операции технологий тонких пленок. Данные термоэлектрические модули именуют тонкопленочными. При наличии обоих типов на рынке возникает важный вопрос о конкуренции двух технологий и изделий, созданных на их основе: является ли новая тонкопленочная технология более прогрессивной, способной вытеснить давно существующую «объемную»? Анализ показывает, что для большинства современных применений объемные термоэлектрические модули, как холодильные, так и генераторные, сохраняют свои преимущества. При внешне кажущихся бесспорными достоинствах тонкопленочных охладителей и генераторов рабочие параметры и эффективность «объемных» модулей заметно выше. За тонкопленочными модулями будущее. В широком диапазоне применений оба типа изделий имеют свои ниши и, если их правильно позиционировать, скорее не конкурируют, а дополняют друг друга.

3Загрузка прошивки через интерфейс JTAG

ПЛИС фирмы Altera поддерживают несколько режимов программирования. Сначала рассмотрим загрузку прошивки в ПЛИС через интерфейс JTAG. Подключите программатор к разъёму JTAG на плате с ПЛИС.

Запустим инструмент для программирования: Tools Programmer.

Добавим программатор. Для этого нажмём кнопку Hardware Setup… и в выпадающем списке выберем подключённый USB Blaster. Закроем окно Hardware Setup.

Настройка программатора

В окне программатора Programmer нажмите кнопку Auto Detect, чтобы Quartus попытался автоматически определить подключённую ПЛИС и файл прошивки *.sof.

Файл прошивки создаётся Квартусом по умолчанию при компиляции и сохраняется в директории output_files, если не задано иное.

В окне Programmer выберите режим JTAG, установите галочку Program/Configure и нажмите кнопку Start. Прошивка будет записана в память ПЛИС.

Загрузка прошивки в ПЛИС через JTAG

Блоки ввода-вывода сигналов.

ПЛИС находят широкое применение благодаря тому, что их можно включать в большинство проектов вычислительных устройств и ими можно заменять большое количество старых микросхем. Предпосылкой этому служит большое число блоков ввода-вывода сигналов IOB, настраиваемых под различные стандарты электрического соединения входов микросхем. На рис. показана структура одного IOB.

Сигнальный вывод ПЛИС получил название PAD. С помощью настройки к нему можно подключать внутренний нагрузочный резистор PULLUP или резистор PULLDOWN, соединенные с шиной питания или шиной земли, соответственно. Эти резисторы обеспечивают режим выхода с открытым коллектором (стоком) для систем с различными уровнями логики. Входной сигнал с PAD поступает на компаратор IBUF, порог срабатывания которого программируется под уровни ТТЛ, КМОП, шины PCI и многие другие, а также может регулироваться установкой подаваемого снаружи напряжения. Для обеспечения временного сдвига сигнала относительно фронта синхросерии, обеспечивающего надежный прием сигнала во внутренние триггеры, в цепь входного сигнала может включаться специальная схема задержки.

Выходной сигнал в IOB формируется в тристабильном буфере OBUFT, причем его уровень максимального тока программируется ступенями и может достигать 20 мА. Для обеспечения быстродействующего ввода-вывода передаваемые и принимаемые биты данных, а также сигнал управления тристабильным буфером могут запоминаться в триггерах.

В новых сериях ПЛИС предусмотрена настройка входного и выходного импеданса PADа, а также бифазное функционирование пар PADов для достижения помехоустойчивой высокоскоростной передачи данных.

При диагностике и отладке, в одном из режимов конфигурирования ПЛИС может быть переключена в режим пограничного сканирования (Boundary Scan). В этом режиме все IOB соединяются в цепочку одного длинного регистра сдвига. Путем стандартного внешнего управления этим регистром сдвига через интерфейс JTAG можно считывать состояния выводов, подавать тестовые сигналы, конфигурировать ПЛИС.

В период конфигурирования ПЛИС для того, чтобы подключаемые к ней устройства не функционировали неопределенным образом, выходы IOB отключаются и на них обычно выставляется уровень H слабой единицы (Weak Keeper).