Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

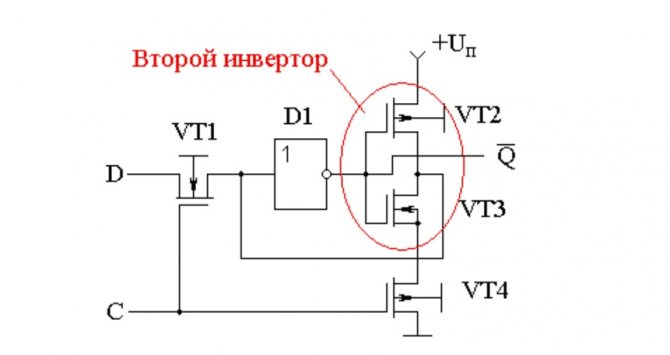

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Схемы запуска триггера

Как говорилось выше для переключения триггера из одного устойчивого состояния в другое необходимо подать на его входы управляющий (запускающий) импульс. В зависимости от того как подавать управляющий импульс существует несколько видов схем запуска триггера:

- 1.В зависимости от способа управления:

- — раздельный способ;

- — счётный (общий) способ.

- 2.В зависимости от места поступления импульса запуска:

- — базовый;

- — коллекторный.

Для запуска триггеров используют короткие импульсы, которые формируются дифференциальными RC- или RL- цепочками. Так как при прохождении импульса через дифференциальную цепочку формируется два разно полярных импульса, то для предотвращения двойного срабатывания триггера между дифференциальной цепочкой и точкой входа запускающего импульса ставят диод, который отсекает второй импульс. В общем случае схема запуска имеет следующий вид:

Схема запуска триггера.

Рассмотрим схему раздельного запуска триггера с подачей управляющих импульсов в базовые цепи транзисторов.

Симметричный триггер с независимым смещением и раздельным запуском.

В данной схеме импульс, поданный на один из входов триггера, переключает его из одного устойчивого состояния в другое. Если импульс подать на другой вход, то состояние триггера изменится на противоположное. Схема запуска состоит из резисторов Rз1 и Rз2, конденсаторов Сз1 и Сз2, диодов VD1 и VD2. Остальные элементы являются цепями питания и смещения транзисторов VT1 и VT2.

Симметричный триггер с раздельным запуском называется RS-триггером, он имеет два входа и два выхода. Входы, на которые подают управляющие импульсы, называются установочными и обозначают R и S, выходы триггера обозначают Q и –Q.

Рассмотрим схему со счётным (общим) запуском триггера и подачей управляющих импульсов в базовые цепи транзисторов.

Симметричный триггер с независимым смещением и счётным запуском.

В данном случае импульсы подаются на общий вход триггера, и каждый импульс приводит к изменению устойчивого состояния триггера. При рассмотрении работы данного типа триггера может возникнуть ощущение, что произойдёт двойное срабатывание, однако за счёт того что у открытого транзистора потенциал базы выше, чем у открытого, то один из диодов сработает раньше другого, а у открытого транзистора диод будет заперт высоким напряжением базы.

Симметричный триггер с общим запуском называется T-триггером и частота переключения данного типа триггера вдвое меньше, чем частота поступающих импульсов запуска.

На процесс перехода триггера из одного состояния в другое существенное значение оказывает время длительности управляющего импульса, например, если импульс имеет недостаточную длительность, то один из транзисторов триггера может не открыться и триггер не сработает.

Использование триггеров

Основная задача, которая решается с помощью таких устройств — с их помощью создается счетчик на D-триггерах. Они отличаются стабильностью своей работы и эффективностью контроля временных функций. Применение D-триггер нашел в промышленном оборудовании, а также в самодельных автоматизированных комплексах, которые работают с применением временных задержек. Хотя могут они использоваться и в других случаях, такая практика не является распространенной, и существует исключительно в целях утоления любопытства конструкторов. Так, создавать регистр на D-триггерах не очень практично, но благодаря дешевизне устройства такая практика довольно распространена.

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние

- 1 RS — триггер

- 1.1 Классическая реализация RS-триггера

- 1.2 Временные диаграммы RS-триггера

- 1.3 Другая реализация RS-триггера

- 2 Синхронный RS-триггер

- 3 Синхронный JK-триггер

- 3.1 Схема JK-триггера

- 3.2 Конкретная реализация синхронного JK-триггера

- 4 D-триггер

- 5 Т-триггер

- 6 Двухступенчатые триггеры

- 6.1 Двухступенчатый синхронный RS-триггер

- 6.2 Двухступенчатый D-триггер

- 6.3 Двухступенчатый JK-триггер

- 7 Универсальные триггеры

- 8 Ступенчатый D-триггер

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Все о законе Ома: простыми словами с примерами для «чайников»

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Как работает JK-триггер

Это электронное устройство работает строго по определённому алгоритму, предусматривающему поступление входных значений и обеспечивающему формирование выходных.

Как видно из схемы, триггер имеет три входа, на которые поступают следующие сигналы:

- J, K — информационные сигналы. Они принимают значение 0 или 1. Каждой комбинации соответствует определённое выходное значение.

- C — двоичный сигнал, который определяет, будут ли меняться выходные сигналы на основании действующего алгоритма или нет. Обычно срабатывание происходит при переходе от единичного к нулевому значению. Также говорят, что срабатывание происходит при отрицательном фронте сигнала.

В этой схеме имеется два выхода:

- Q — прямой. Выдает значение, которое на данный момент хранится в триггере.

- Q1 также обозначают как Q с горизонтальной чертой сверху — инверсный. Этот сигнал всегда будет противоположным по отношению к Q.

JK-триггер — это своего рода усовершенствованный RS-триггер. В последнем наблюдается одно запрещённое состояние, использование которого приводит к неопределённому результату на выходе. В JK-устройстве такое состояние исключено. В остальном оба элемента действуют аналогично.

JK-триггер — универсальное устройство. На его базе можно построить простой и асинхронный Т-триггер, D-триггер, синхронный RS-триггер

Есть еще комбинированный JK-триггер. От универсального он отличается двумя дополнительными асинхронными входами S и R. Последние позволяют предварительно установить устройство в определенный режим (логического нуля или единицы).

Принцип работы RS триггера

Система, представленная выше, при помощи электромагнитных реле иллюстрирует работу триггера на элементах ИЛИ-НЕ. Однако в современных схемах электромеханические приборы давным-давно не используются, сейчас они собираются из электронных логических элементов на транзисторах, заключенных внутри интегральных микросхем. К тому же для их реализации можно использовать различные базисы. Пример схемы RS триггера на элементах И-НЕ, охваченных положительной обратной связью.

Допустим, что на оба входа R и S подаются единицы. Если верхний элемент И-НЕ выдаст на прямой выход Q логический 0, благодаря положительной обратной связи он поступит на свободный вход нижнего элемента, вследствие чего тот выдаст на инверсном выходе единицу (1). В свою очередь, эта 1 по обратной связи поступает на вход верхнего элемента, тем самым подтверждая 0 на выходе Q. Если же на прямом выходе изначально находится 1, то инверсный, соответственно, выдаст 0, который подтвердит 1 на выходе Q.

Транзисторная схема RS триггера

При подаче на S-вход 0, согласно логической функции И-НЕ, на прямом выходе Q возникнет 1, а на инверсном – 0. Если при этом на вход S снова подать 1, состояние триггера не изменится, так как по таблице истинности И-НЕ при подаче на входы элемента комбинации 0 и 1 либо 0 и 0, на выходе всегда будет 1. Таким образом, триггерная схема сохраняет полученное значение неизменным. Сбросить значение Q обратно в 0 можно, только подав сигнал на сбрасывающий вход R. Практически работу RS триггера можно пронаблюдать, собрав такую схему на транзисторах.

Принцип работы

Устаревшие элементы учёта затраченной электроэнергии

Во всех схемах имеет значение длительность рабочих реакций, которая определяет время записи (стирания). Определенное значение имеет помехоустойчивость. В следующих разделах рабочие процессы рассмотрены подробно.

Элементы с управлением по уровню

В этом варианте изменение состояния происходит только при высоком уровне синхронизирующего сигнала. При соответствующем положении устройство копирует изменения на входе с небольшой технологической задержкой. Если на С – ноль, реакция на выходе отсутствует.

Временная диаграмма для управления триггером по уровню

Элементы с управлением по фронту

В соответствии с названием, здесь реализована схема управления по фронту (переднему и заднему). С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

Изменение состояния при разных информационных (управляющих) сигналах

Допустим, что для управления выбран передний фронт. При С=0 состояние триггера не изменяется, вне зависимости от информационных сигналов, – одновременно с прохождением переднего фронта записывается аналогичное уровню D. В данном примере – единица. Следующие изменения происходят по такому же алгоритму.

Чтобы расширить базовую функциональность, устройство дополняют представленными выше сервисными входами (R и S). С их помощью состояние устанавливают произвольным образом (1 или 0) в любой нужный момент. Разумеется, для выполнения таких действий понадобятся дополнительные элементы управления.

К сведению. В этом варианте не имеет значения длительность управляющего сигнала. Для функционирования схемы его можно подать с применением инвертора в противофазе на два триггера Д типа, соединенные последовательно. Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

Триггеры. RS-триггеры. Асинхронный RS-триггер с инверсными входами

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер имеет два выхода: прямой Q

и инверсный. Состояние триггера определяют по значению сигнала на прямом выходеQ. Значения сигналов на прямом и инверсном выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

1.RS-триггеры ‘АсинхронныеRS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. АсинхронныеRS -триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS

-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входаS иR.. По входуS триггер устанавливается в состояниеQ =1( =0), по входуR— в состояниеQ =0(= 1). В зависимости от логической структуры асинхронныеRS -триггеры бывают с прямыми либо инверсными входами и могут строиться на двух логических элементах: 2ИЛИ-НЕ — триггер с прямыми входами; или на элементах 2И-НЕ — триггер с инверсными входами.

АсинхронныйRS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q

и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

Временные диаграммы, характеризующие работу асинхронного RS

-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R

=S =0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (R и S) приводит к неопределенности. На обоих выходахQи появляются единицы, а после отключения входов (S=R=0) может установиться любое состояние

JK-триггер. Принцип работы, фунцкциональные схемы, таблицы истинности

Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов.

Симметричный триггер с автоматическим смещением.

Кроме схем триггеров с внешним смешением существует ряд схем с автоматическим смещением, которое создается за счёт падения напряжения на сопротивлении Re в цепях эмиттеров транзисторов VT1 и VT2.

Симметричный триггер с автоматическим смещением.

Кроме резистора Re в цепи эмиттеров включается конденсатор Се, который выбирается достаточно большой ёмкости, чтобы за время переключения триггера из одного состояния в другое напряжение смещения практически не менялось. За счёт элементов Re и Се отпадает необходимость в отдельном источнике напряжения смещения, но это же приводит к тому что уменьшается уровень напряжения, которое может быть снято с выходов триггера. Кроме того на сопротивлении Re рассеивается достаточно большая мощность. В остальном же параметры схемы практически идентичны и схема с автоматическим смещением так же как схема с внешним смещением может использоваться как с раздельным запуском, так и с общим запуском.

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.