Функции регистров АЛУ

Чтобы иметь представление о работе АЛУ, нам нужно поближе познакомиться с функциями его регистров:

- Pr1. Это аккумулятор или аккумуляторы. Считается главным регистром устройства, в котором и образуется результат произведенных вычислений.

- Pr2, Pr3. Регистры операндов в зависимости от характера исполняемой операции — слагаемого, делителя, сомножителя и проч.

- Pr4. Это адресный регистр. Он запоминает (в иных случаях формирует) адреса операндов результата.

- Pr6. Некое количество индексных регистров. Их содержимое будет использоваться для формирования адресов.

- Pr7. Вспомогательные регистры. По желанию разработчика могут стать аккумуляторами, индексными или вовсе использоваться для сохранения промежуточных результатов вычисления.

Теперь предлагаем вам обратиться к конкретным алгоритмам работы АЛУ.

Организация и принципы действия

Одноразрядное троичное бинарное (двухоперандное) АЛУ с унарным (одноразрядным) выходом (полуАЛУ) может выполнять до троичных бинарных (двухоперандных) функций (операций) с унарным (одноразрядным) выходом.

Одноразрядное троичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до троичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство, в котором реализуется заданная последовательность микрокоманд (команд).

В состав арифметико-логического устройства, условно, для примера на картинке, включается регистры Рг1 — Рг7, которые служат для обработки информации, поступающей из оперативной или пассивной памяти N1, N2, …NS и логические схемы, которые используются для обработки слов по микрокомандам, поступающим из устройства управления. Различают два вида микрокоманд: внешние — такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нём преобразование информации (на рисунке 2 это микрокоманды А1,А2,…,Аn) и внутренние — те, которые генерируются в АЛУ и оказывают влияние на микропрограммное устройство, изменяя таким образом нормальный порядок следования команд. р1, p2,…, pm на рисунке 2 — это и есть микрокоманды. А результаты вычислений из АЛУ передаются в ОЗУ по кодовым шинам записи у1, у2, …, ys.

Функции регистров, входящих в арифметико-логическое устройство

- Рг1 — аккумулятор (или аккумуляторы) — главный регистр АЛУ, в котором образуется результат вычислений;

- Рг2,Рг3 — регистры операндов (слагаемого/сомножителя/делителя/делимого и др.) в зависимости от выполняемой операции;

- Рг4 — регистр адреса (или адресные регистры), предназначенные для запоминания (бывает что формирования) адреса операндов результата;

- Рг6 — k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 — l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров могут быть адресованы в команде для выполнения операций с их содержимым и их называют программно-доступными. К таким регистрам относятся: сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, то есть они являются программно-недоступными.

Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу её обработки и по логической структуре. Более подробная классификация указана на рис.3.

Такая сложная логическая структура АЛУ может характеризоваться количеством отличающихся друг от друга микроопераций, которые необходимы для выполнения всего комплекса задач, поставленных перед арифметико-логическим устройством. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяет реализовать заданные микрооперации. Выполнение операций над словами сводится к выполнению определённых микроопераций, которые сводятся в свою очередь … управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. То есть, связи между регистрами АЛУ и их функциями зависят в основном от принятой методики выполнения логических операций, в том числе арифметических или специальной арифметики.

Ссылки [ править ]

- ^

- ^ . Штаб, Управление армии. 2001. С. 371–.

- ^ А.П. Годсе; ДАГодсе (2009). «Приложение». . Технические публикации. стр. C – 1. ISBN

- . www.oreilly.com . Проверено 3 сентября 2020 .

- Горовиц, Пол ; Уинфилд Хилл (1989). «14.1.1». Искусство электроники (2-е изд.). Издательство Кембриджского университета. С. 990-. ISBN 978-0-521-37095-0.

- Филип Левис (8 ноября 2004 г.). . cs.berkeley.edu . С. 1, 3. Архивировано из 23 сентября 2015 года . Проверено 20 января 2015 года .

- Ли Бойсел (2007-10-12). . Презентация EECS США / Записи ЕЭК . Архивировано из на 2012-11-15.

- Рейф, Джон Х. (2009), Мейерс, Роберт А. (редактор), , Энциклопедия сложности и системной науки , Нью-Йорк, Нью-Йорк: Springer, стр. 5466– 5482, DOI , ISBN

- Линь, Чунь-Лян; Куо, Тинг-Ю; Ли, Вэй-Сянь (2018-08-14). . Журнал биологической инженерии . 12 (1): 14. DOI . ISSN . PMC . PMID .

- Герд Hg Moe-Behrens. .

- Дас, Биплаб; Пол, Авиджит Кумар; Де, Дебашис (2019-08-16). . Микросистемные технологии . DOI . ISSN .

Сигналы [ править ]

ALU имеет множество входных и выходных цепей , которые представляют собой электрические проводники, используемые для передачи цифровых сигналов между ALU и внешней схемой. Когда ALU работает, внешние схемы подают сигналы на входы ALU, и в ответ ALU вырабатывает и передает сигналы во внешние схемы через свои выходы.

Данные редактировать

Базовый ALU имеет три параллельные шины данных, состоящие из двух входных операндов ( A и B ) и вывода результата ( Y ). Каждая шина данных представляет собой группу сигналов, передающих одно целое двоичное число. Обычно ширина шины A, B и Y (количество сигналов, составляющих каждую шину) идентична и соответствует собственному размеру слова внешней схемы (например, инкапсулирующего ЦП или другого процессора).

Код операции править

Опкод вход параллельной шины , который передает АЛУ операции выбора кода, который представляет собой перечислимое значение , которое указывает желаемый арифметической или логической операции , которые должны выполняться АЛУ. Размер кода операции (его ширина шины) определяет максимальное количество различных операций, которые может выполнять ALU; например, четырехбитовый код операции может определять до шестнадцати различных операций ALU. Как правило, код операции ALU отличается от кода операции машинного языка , хотя в некоторых случаях он может быть напрямую закодирован как битовое поле внутри кода операции машинного языка.

Выходы править

Выходы состояния — это различные отдельные сигналы, которые передают дополнительную информацию о результате текущей операции ALU. У ALU общего назначения обычно есть такие сигналы состояния, как:

- Выполнение , которое передает перенос, полученный в результате операции сложения, заимствования в результате операции вычитания или бит переполнения в результате операции двоичного сдвига.

- Ноль , который указывает, что все биты Y равны логическому нулю.

- Отрицательный , что указывает на отрицательный результат арифметической операции.

- Переполнение , указывающее, что результат арифметической операции превышает числовой диапазон Y.

- Четность , которая указывает, является ли четное или нечетное количество бит в Y логической единицей.

По завершении каждой операции ALU выходные сигналы состояния обычно сохраняются во внешних регистрах, чтобы сделать их доступными для будущих операций ALU (например, для реализации арифметики с высокой точностью ) или для управления условным переходом . Набор битовых регистров, в которых хранятся выходные данные состояния, часто рассматривается как один многобитовый регистр, который называется «регистром состояния» или «регистром кода состояния».

Входы править

Входы состояния позволяют сделать доступной дополнительную информацию для ALU при выполнении операции. Обычно это единственный бит переноса, который является сохраненным переносом из предыдущей операции ALU.

Функции [ править ]

ALU обычно поддерживает ряд основных арифметических и побитовых логических функций. Базовые ALU общего назначения обычно включают в свой репертуар следующие операции:

Арифметические операции править

- : A и B суммируются, и сумма появляется в Y и переносится.

- Сложение с переносом : A, B и перенос суммируются, и сумма отображается в Y и переносе.

- : B вычитается из A (или наоборот), а разница появляется в Y и переносе. Для этой функции выполнение фактически является индикатором «заимствования». Эту операцию также можно использовать для сравнения величин A и B; в таких случаях выход Y может игнорироваться процессором, который интересуется только битами состояния (в частности, нулевым и отрицательным), которые возникают в результате операции.

- Вычесть с заимствованием : B вычитается из A (или наоборот) с заимствованием (переносом), а разница появляется в Y и переносе (заимствовании).

- Дополнение до двух (отрицание) : A (или B) вычитается из нуля, и разница появляется в Y.

- Приращение : A (или B) увеличивается на единицу, и результирующее значение появляется в Y.

- Уменьшение : A (или B) уменьшается на единицу, и результирующее значение появляется в Y.

- Проходить : все биты A (или B) отображаются без изменений в Y. Эта операция обычно используется для определения четности операнда, равно нулю или отрицательности, или для загрузки операнда в регистр процессора.

Побитовые логические операции править

- : побитовое И для A и B появляется в Y.

- : побитовое ИЛИ A и B появляется в Y.

- : побитовое исключающее ИЛИ A и B появляется в Y.

- : все биты A (или B) инвертируются и появляются в Y.

Операции битового сдвига править

| Тип |

Оставили |

Правильно |

|---|---|---|

| Арифметический сдвиг |

||

| Логический сдвиг |

||

| Повернуть |

||

| Повернуть через перенос |

Операции сдвига ALU заставляют операнд A (или B) сдвигаться влево или вправо (в зависимости от кода операции), и смещенный операнд появляется в Y. Простые ALU обычно могут сдвигать операнд только на одну битовую позицию, тогда как более сложные ALU используют цилиндрические сдвиги , позволяют им сдвигать операнд на произвольное количество бит за одну операцию. Во всех операциях однобитового сдвига бит, смещенный из операнда, появляется при выполнении; значение сдвигаемого в операнд бита зависит от типа сдвига.

- : операнд обрабатывается какцелое число с дополнением до двух , что означает, что самый старший бит является «знаковым» битом и сохраняется.

- : в операнд сдвигается логический ноль. Используется для сдвига целых чисел без знака.

- : операнд обрабатывается как кольцевой буфер битов, поэтому его младший и самый старший биты фактически смежны.

- : бит переноса и операнд вместе рассматриваются как кольцевой буфер битов.

Операция вычитания

Давайте рассмотрим выполнение еще одной простой арифметической операции:

- Значение операнда № 1, принимающего участие в операции вычитания, проходит в Регистр 1 по кодовой шине.

- Значение операнда № 2, принимающего участие в операции вычитания, проходит в Регистр 2 по кодовой шине.

- Инструкция по выполнению данного алгоритма выводится по кодовой шине инструкций к схеме управления.

- Происходит переформирование положительного числа в отрицательное схемой управления.

- Результат такого преобразования операнда идет далее в сумматор.

- Сумматор выполняет сложение данных чисел.

- Результат операции поступает в Регистр 1.

- Результат операции вычитания отправляется в результирующий блок.

Литература[править | править код]

- Каган Б. М. Электронные вычислительные машины и системы. — 3-е изд., перераб. и доп. — Энергоатомиздат, 1991. — ISBN 5-283-01531-9.

- Угрюмов Е. П. Цифровая схемотехника. Учеб. пособие для вузов. Изд. 2. — БХВ-Петербург, 2004.

- Самофалов К. Г., Романкевич А. М., Валуйский В. Н., Каневский Ю. С., Пиневич М. М. Прикладная теория цифровых автоматов. — К.: Вища школа, 1987. — С. 375.

- Ершов А. П., Монахов В. М., Бешенков С. А. и др. 1 // Основы информатики и вычислительной техники: Проб. учеб. пособие для сред. учеб. заведений. В 2 ч. — М.: Просвещение, 1985. — С. 96.

- Ершов А. П., Монахов В. М., Кузнецов А. А. и др. 2 // Основы информатики и вычислительной техники: Проб. учеб. пособие для сред. учеб. заведений. В 2 ч. — М.: Просвещение, 1986. — С. 143.

Классификация АЛУ

- По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

-

По способу представления чисел различают АЛУ:

- для чисел с фиксированной точкой;

- для чисел с плавающей точкой;

- для десятичных чисел.

- По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

- По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметическо-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные: move , input , outptut , load и store .

- Команды перехода: goto , if . goto , call и return .

- Команда останова: halt .

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Операции в АЛУ

Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»). Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ, четверичной логикой для четверичных ЭВМ, …, десятичной логикой для десятичных ЭВМ и т. д..

История

Математик Джон фон Нейман предложил концепцию ALU в 1945 году в отчете об основах нового компьютера под названием EDVAC.

Стоимость, размер и потребляемая мощность электронных схем были относительно высокими на протяжении всего периода становления. информационный век. Следовательно, все последовательные компьютеры и многие ранние компьютеры, такие как PDP-8, имели простой ALU, который работал с одним битом данных за раз, хотя они часто предоставляли программистам более широкий размер слова. Одним из первых компьютеров с несколькими дискретными однобитными схемами ALU был компьютер 1948 года. Вихрь I, в котором использовалось шестнадцать таких «математических модулей», позволяющих оперировать 16-битными словами.

В 1967 г. Fairchild представила первый ALU, реализованный в виде интегральной схемы, Fairchild 3800, состоящий из восьмиразрядного ALU с аккумулятором. Вскоре появились другие ALU на интегральных схемах, в том числе четырехразрядные ALU, такие как Am2901 и . Эти устройства обычно «кусочек«способный» означает, что у них были сигналы «с упреждением», которые облегчили использование нескольких взаимосвязанных микросхем ALU для создания ALU с более широким размером слова. Эти устройства быстро стали популярными и широко использовались в мини-компьютерах с побитовым срезом.

Микропроцессоры начали появляться в начале 1970-х годов. Несмотря на то, что транзисторы стали меньше, часто не хватало места на кристалле для ALU полной ширины слова, и, как результат, некоторые ранние микропроцессоры использовали узкий ALU, который требовал нескольких циклов для каждой инструкции машинного языка. Примеры этого включают популярные Зилог Z80, который выполнял восьмибитное сложение с четырехбитным ALU. Со временем геометрия транзисторов еще больше уменьшилась. Закон Мура, и стало возможным создавать более широкие ALU на микропроцессорах.

Транзисторы современных интегральных схем (ИС) на порядки меньше, чем транзисторы ранних микропроцессоров, что позволяет устанавливать очень сложные АЛУ на ИС. Сегодня многие современные ALU имеют большую ширину слова и архитектурные улучшения, такие как баррель шифтеры и двоичные множители которые позволяют им выполнять за один такт операции, которые потребовали бы нескольких операций на более ранних ALU.

ALU могут быть реализованы как механический, или же электронный схемы[неудачная проверка] а в последние годы были проведены исследования биологических ALU. (например., актин-основан).

Работа схемы [ править ]

Комбинационная логическая схема из интегральной схемы, которая является простым четыре бита ALU

ALU — это комбинационная логическая схема, что означает, что его выходы будут изменяться асинхронно в ответ на изменения входа. В нормальном режиме работы стабильные сигналы подаются на все входы ALU, и, когда прошло достаточно времени (известное как « задержка распространения ») для распространения сигналов через схему ALU, результат работы ALU появится на ALU. выходы. Внешняя схема, подключенная к ALU, отвечает за обеспечение стабильности входных сигналов ALU на протяжении всей операции и за обеспечение достаточного времени для распространения сигналов через ALU перед выборкой результата ALU.

Как правило, внешняя схема управляет ALU, подавая сигналы на его входы. Как правило, внешняя схема использует последовательную логику для управления работой ALU, которая регулируется тактовым сигналом достаточно низкой частоты, чтобы обеспечить достаточно времени для выхода ALU для стабилизации в худших условиях.

Например, ЦП начинает операцию добавления ALU, направляя операнды из их источников (которые обычно являются регистрами) на входы операндов ALU, в то время как блок управления одновременно применяет значение ко входу кода операции ALU, настраивая его для выполнения сложения. В то же время ЦП также направляет вывод результата ALU в регистр назначения, который получит сумму. Входные сигналы ALU, которые остаются стабильными до следующих часов, могут распространяться через ALU и в регистр назначения, пока CPU ожидает следующих часов. Когда приходят следующие часы, регистр назначения сохраняет результат ALU, и, поскольку операция ALU завершена, входы ALU могут быть настроены для следующей операции ALU.

Общие сведения об арифметико логическом устройстве

Арифметико логическое устройство — это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции:

- принимающая на два входа два операнда (например, содержимое двух регистров);

- формирующая на выходе результат операции.

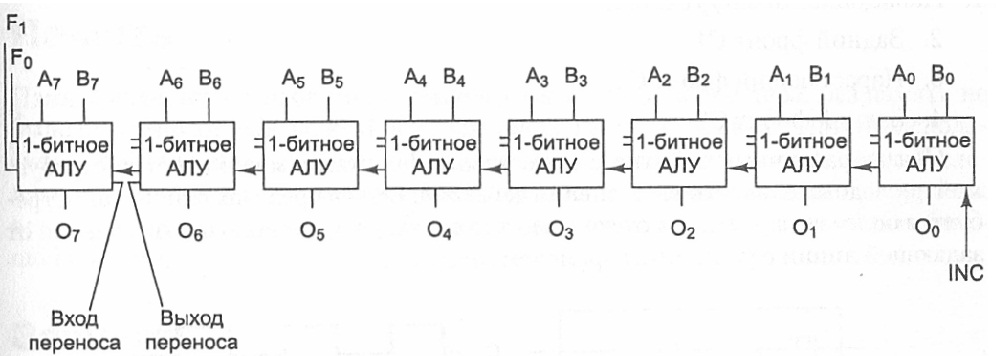

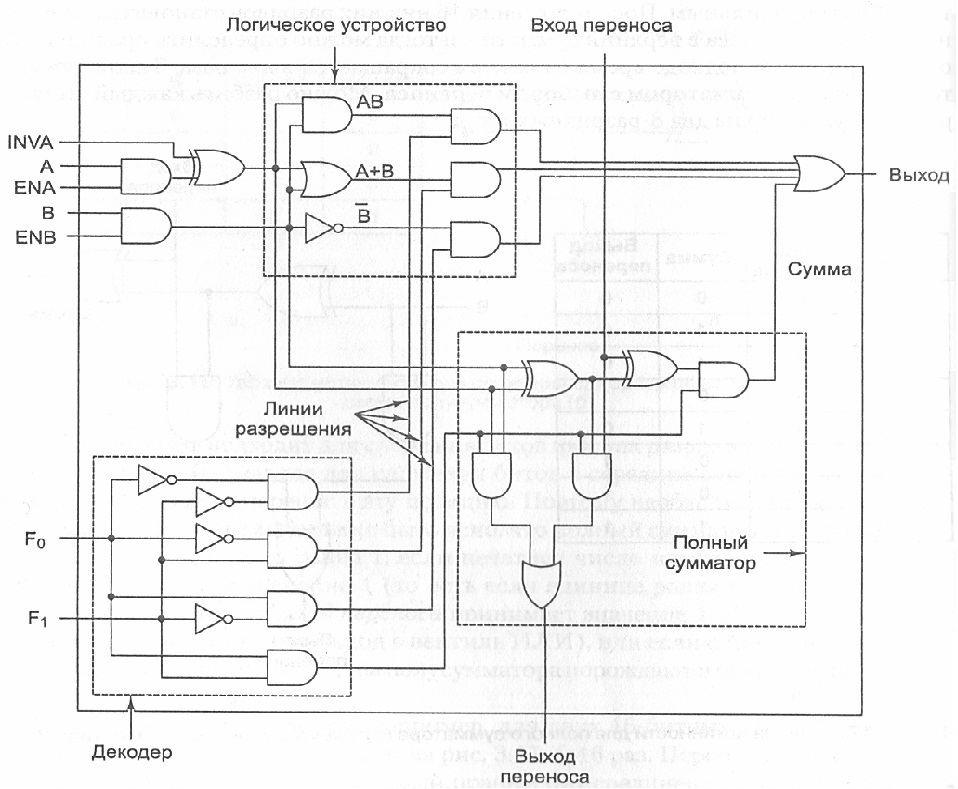

Большинство компьютеров содержат одну общую схему для выполнения операций И, ИЛИ и сложения над двумя машинными словами. Обычно такая схема для n-битных слов состоит из n идентичных схем для индивидуальных битовых позиций. На рисунке изображена схема одноразрядного АЛУ. Это устройство может вычислять одну из 4 следующих функций: А И В, А ИЛИ В, В- и А + В. Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1: 00, 01, 10 или 11 (в двоичной системе счисления). Отметим, что здесь А+В означает арифметическую сумму А и В, а не логическую операцию И. В левом нижнем углу схемы находится двухразрядный декодер, который порождает сигналы включения для четырех операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ. В верхнем левом углу схемы находится логическое устройство для вычисления А И В, А ИЛИ В и В-, но по крайней мере, один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И.

Схема одноразрядного АЛУ

Остальные три вентиля будут выдавать 0 независимо от значений А и В.АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить А-, установив INV А (инверсию А). При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INV А равен 0. В этом случае А и В просто поступают в логическое устройство без изменений. В нижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами. Одноразрядные схемы, подобные той, которая изображена выше, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. АЛУ можно представить как комбинационную схему, имеющую две входные шины (туда подаются два операнда) и одну выходную (на ней получается результат). Кроме того, АЛУ имеет несколько управляющих входов, сигналы на которых определяют выполняемую операцию(рисунок ниже).