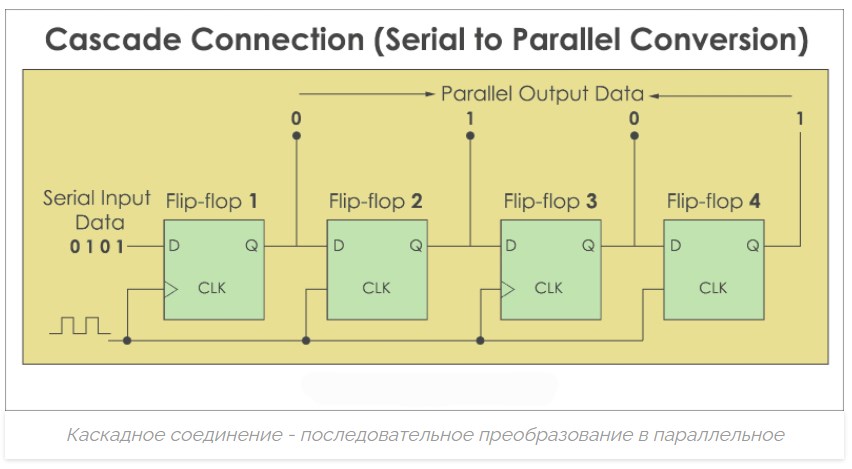

Последовательное преобразование в параллельное

Шаг 1: Возьмем 4 триггера. Количество триггеров совпадает с количеством передаваемых битов.

Шаг 2: Сначала отключим параллельную шину. Не включаем пока не будут загружены все биты. Сохраним данные на входе первого триггера. Теперь установим высокий уровень тактовой частоты, это сдвинет младший бит на вход второго триггера и выход первого. Точно так же сдвинем все биты один за другим, сделав тактовый импульс высоким. Преобразователь находится в состоянии удержания до тех пор, пока все биты не будут переданы на выход.

Шаг 3: Теперь каждый триггер содержит один бит последовательных данных. Пока все биты передаются на выход триггера, активируем шину. Это заставит конвертер отправлять все биты за раз.

Что у меня получилось

Я решил по-максимуму задействовать возможности периферии микроконтроллера, но вместе с тем не впадать в пучину предварительных оптимизаций. Читаемость и поддерживаемость кода для меня гораздо важнее, чем незначительный прирост производительности. Тем более, что с производительностью и так все вышло очень хорошо.

Что реализовано:

- три независимых последовательных порта;

- поддержка аппаратного контроля потока (RTS/CTS) на двух из трех портов;

- поддержка управляющих сигналов DSR/DTR/DCD/RI;

- поддержка 7 и 8-битной длины слова;

- поддержка контроля четности;

- 1, 1.5 и 2 стоповых бита;

- совместимость со стандартными драйверами Linux, macOS и Windows;

- подписанный INF файл для Windows XP, 7 и 8;

- поддержка произвольных скоростей (более 2 Мбит/с);

- сигнал TXA для управления трансиверами RS-485 (DE, /RE);

- DMA на передачу и прием данных USART;

- встроенный командный интерпретатор для конфигурации;

- нет зависимостей от сторонних библиотек кроме CMSIS;

- проект с открытым исходным кодом, лицензия MIT;

Командный интерпретатор позволяет настраивать следующие параметры:

- тип выхода: двухтактный, открытый сток;

- тип подтяжки входных линий: вверх, вниз, плавающая;

- инверсия для управляющих сигналов: активный высокий/низкий;

Командный интерпретатор активируется на первом CDC порту при подключении пина PB5 к земле, поддерживает часть управляющих последовательностей ANSI (стрелочки, backspace), и принимает вполне дружелюбные на вид команды:

Командный интерпретатор не позволяет переназначать сигналы с одних пинов на другие. Во-первых, далеко не все сигналы можно переназначить, а во-вторых, такая возможность по-настоящему становится востребованной только при использовании прошивки в контексте какой-либо иной платы. В этом случае проще и правильнее переназначить сигналы используя конфигурацию, хранящуюся в исходном коде.

Распиновка вышла следующей:

| Signal | Direction | UART1 | UART2 | UART3 |

|---|---|---|---|---|

| RX | IN | PA10 | PA3 | PB11 |

| TX | OUT | PA9 | PA2 | PB10 |

| RTS | OUT | N/A | PA1 | PB14 |

| CTS | IN | N/A | PA0 | PB13 |

| DSR | IN | PB7 | PB4 | PB6 |

| DTR | OUT | PA4 | PA5 | PA6 |

| DCD | IN | PB15 | PB8 | PB9 |

| RI | IN | PB3 | PB12 | PA8 |

| TXA | OUT | PB0 | PB1 | PA7 |

Пины, выделенные жирным шрифтом, являются толерантными к 5 В.

Сигнал TXA (TX Active) служит для управления микросхемами трансиверов RS-485 (DE, /RE). TXA активен во время передачи данных и переключается в неактивное состояние не более чем за 0.6 мкс после завершения передачи. Это соответствует спецификациям RS-485 на скоростях до 920 кБод c почти двукратным запасом по времени переключения.

К сожалению, реализовать RTS/CTS на UART1 не вышло из-за того, что соответсвующие пины заняты сигналами USB. Можно было вывести RTS на какой-нибудь другой пин, поскольку RTS управляется программно, в зависимости от степени заполнения кольцевых буферов на прием, но порт c RTS и без CTS мне показался странной штукой и я решил, что так делать не надо.

Проект написан на языке C, и подразумевает использование arm-none-eabi-gcc для сборки. Я использовал специфичный для GCC синтаксис атрибутов и расширения языка С. Совместимость проекта с проприетарными компиляторами меня не интересует, но если кто-то считает это важным, то я готов принять соответствующий пул-реквест.

В результате у меня получилось удобное и мощное устройство которое полностью закрывает все мои потребности в последовательных портах. STM32 Blue Pill можно использовать как самостоятельно, так и в составе схем обеспечивающих согласование уровней и развязку. Возможность настройки сигнальных линий позволяет упростить разработку таких схем.

UART

Универсальный асинхронный приемник / передатчик, обычно называемый UART, представляет собой асинхронный приемник / передатчик, который является частью компьютерного оборудования. Он будет передавать данные вПоследовательная связьпротивПараллельное общениеЧтобы преобразовать между. Как микросхема, преобразующая параллельные входные сигналы в последовательные выходные сигналы, UART обычно интегрируется в соединение с другими интерфейсами связи.

Последовательный порт во встроенной системе обычно относится к порту UART, но мы часто не знаем разницы между ним и COM-портом, а также отношения между RS232, TTL и т. Д. Фактически, UART, COM относятся к форме физического интерфейса (аппаратного), а TTL, RS-232 относится к стандарту уровня (электрический сигнал).

UART имеет 4 контакта (VCC, GND, RX, TX), используя уровень TTL, низкий уровень — 0 (0 В), высокий уровень — 1 (3,3 В или выше).

Особенности UART: Как правило, контроллеры uart создаются вместе с процессорами во встроенных системах.Как и микросхема Freescale IMX6, существует несколько контроллеров uart.

Введение в интерфейс SPI

В последние несколько дней я наткнулся на флэш-память, использующую интерфейс SPI, и знаю, что флэш-память также может быть последовательной. Кажется, что это действительно была лягушка на дне колодца. Я нашел некоторую информацию об интерфейсе SPI. Позже я нашел информацию на английском языке, перевел ее и добавил Мое личное понимание было собрано в статью, надеюсь, она будет полезна новичкам.

Полное название интерфейса SPI — «Serial Peripheral Interface», что означает последовательный периферийный интерфейс. Впервые он был определен компанией Motorola для процессоров серии MC68HCXX. Интерфейс SPI в основном используется между EEPROM, FLASH, часами реального времени, аналого-цифровым преобразователем, процессором цифрового сигнала и декодером цифрового сигнала.

Интерфейс SPI — это синхронная последовательная передача данных между ЦП и периферийными низкоскоростными устройствами. Под импульсом сдвига ведущего устройства данные передаются в битах, старший бит находится спереди, а положение — сзади. Это полнодуплексная связь, и скорость передачи данных общая. Он быстрее шины I2C, а скорость может достигать нескольких Мбит / с.

Интерфейс SPI работает в режиме ведущий-ведомый. В этом режиме обычно есть ведущее устройство и одно или несколько ведомых устройств. Интерфейс включает следующие четыре сигнала:

(1) Вывод данных MOSI-ведущего устройства, ввод данных ведомого устройства

(2) Ввод данных MISO-ведущего устройства, вывод данных ведомого устройства

(3) Сигнал SCLK-clock, генерируемый ведущим устройством.

(4) / SS — сигнал включения ведомого устройства, управляемый ведущим устройством

В двухточечной связи интерфейс SPI не требует операций адресации и является полнодуплексным, что является простым и эффективным.

В системе с несколькими подчиненными устройствами каждое подчиненное устройство нуждается в независимом разрешающем сигнале, который немного сложнее аппаратно, чем система I2C.

Интерфейс SPI на самом деле представляет собой два простых регистра сдвига во внутреннем оборудовании.Передаваемые данные составляют 8 бит.Под сигналом включения ведомого и импульсом сдвига, генерируемым ведущим устройством, он передается бит за битом, причем старший бит находится спереди, а младший бит — сзади. . Как показано на рисунке ниже, данные изменяются по заднему фронту SCLK, и в то же время в регистре сдвига сохраняется один бит данных.

Схема внутреннего оборудования интерфейса SPI:

Наконец, один недостаток интерфейса SPI: нет назначенного управления потоком и нет механизма ответа, подтверждающего, получены ли данные.

Пример интерфейса UART

Этот пример демонстрирует взаимодействие ESP8266 UART с MAX232. Микросхема MAX232 питается от источника 5 В, и включает в себя генератор емкостного напряжения для управления напряжением 232 уровня. Она поставляется с двумя передатчиками, также называемыми драйвером (Tin, Tout) и приемниками (Rin и Rout).

Здесь использовался ESP8266 (32-битный микроконтроллер) со встроенным UART. Связь может осуществляться с ESP8266 с использованием AT-команд через преобразователь уровня RS232 в TTL (MAX232). На схеме показано подключение ESP8266 к компьютеру.

Запрашивая действительные AT-команды через ПК, микросхема Wi-Fi ответит подтверждением. Вот шаги для реализации последовательной связи с ПК.

- Подключить передатчик (TX) ESP8266 к приемнику (RX) преобразователя уровня RS232 в TTL (MAX232) и приемника ПК.

- Подключить приемник (RX) ESP8266 к TX ПК и RX преобразователя TTL.

SPI (Serial Peripheral Interface)

Это протокол последовательной связи синхронного типа, который состоит из двух линий данных (MOSI и MISO), одной тактовой линии (SCK) и линии выбора подчиненных (SS).

Перед тем, как двигаться дальше, нужно прояснить значения несколько терминов, которые вы должны знать:

Master (ведущий) — устройство, которое обеспечивает синхронизацию

Slave (ведомый) — устройство, отличное от мастера, использующее тактирование ведущего для связи

MOSI — Master Out Slave In (линия, по которой мастер отправляет данные своим подчиненным)

MISO — Master In Slave Out (линия, по которой ведомые передают ведомому данные в ответ)

SCK – линия тактирования (предоставляется ведущим устройством)

SS — Slave Select (линия, используемая для выбора ведомого устройства, к которому ведущий хочет установить связь)

В случае с SPI в любой момент времени может быть только одно ведущее устройство и несколько других ведомых, которые отвечают только на вызов ведущего. Вся связь обрабатывается самим ведущим; ни один подчиненный не может отправлять данные по своей воле. Ведущий отправляет данные через MOSI, а ведомые отвечают через линию MISO. Во всем процессе SCK (последовательное тактирование) играет очень важную роль, каждое подчиненное устройство зависит от этих часов, чтобы читать данные из MOSI и отвечать через MISO. SS (выбор ведомого) используется для того, чтобы конкретное подчиненное устройство проснулось, с кем мастер хочет общаться. Ниже представлена иллюстрация принципа подключения посредством интерфейса SPI:

Существует несколько регистров, которые используются для реализации связи SPI. Все нижеперечисленные регистры имеют длину 8 бит.

SPDR (регистр данных SPI) используется для хранения одного байта данных, который должен быть передан или получен.

SPSR (регистр состояния SPI) содержит биты состояния, участвующие в передаче SPI.

SPCR (регистр управления SPI) содержит контрольные биты, участвующие в передаче SPI.

Преимущества интерфейса SPI следующие. Во-первых он обеспечивает синхронную последовательную связь, которая намного надежнее асинхронной. Во-вторых, несколько устройств (ведомые устройства) могут быть подключены к одному ведущему устройству. В-третьих, это быстрая форма последовательной связи.

Недостатки SPI следующие. Во-перых, требуется несколько линий выбора ведомых для подключения нескольких подчиненных устройств. Во-вторых, только ведущий контролирует весь процесс коммуникации; никакие подчиненные не могут напрямую связываться друг с другом.

Возможности и характеристики

Как вы, наверное, знаете, базовая система UART обеспечивает надежную, среднескоростную, полнодуплексную связь только с тремя сигналами: Tx (последовательно передаваемые данные), Rx (последовательно принимаемые данные) и земля. В отличие от других протоколов, таких как SPI и I2C, в нем не требуется никаких сигналов синхронизации, так как пользователь дает аппаратному обеспечению UART необходимую для синхронизации информацию.

Связь двух микроконтроллеров через UART

На самом деле, сигнал синхронизации существует, но он не передается от одного устройства связи к другому; и приемник, и передатчик имеют внутренние тактовые сигналы, которые управляют тем, как изменение логических уровней генерируется (на стороне Tx) и интерпретируется (на стороне Rx). Неудивительно, что связь через UART не работает, если передатчик и приемник настроены на разные частоты передачи данных. Кроме того, внутренние тактовые сигналы должны быть:

- достаточно точны и близки к ожидаемой частоте;

- достаточно стабильны в течение долгого времени и изменений температуры.

Ключевые термины

Давайте рассмотрим некоторые термины и попутно характеристики UART:

- Стартовый бит

- Первый бит в передаче одного байта через UART. Он указывает на то, что линия данных покидает состояние ожидания. В состоянии ожидания, как правило, на линии установлен высокий логический уровень, поэтому стартовый бит равен низкому логическому уровню. Стартовый бит является вспомогательным, это означает, что он обеспечивает связь между приемником и передатчиком, но не передает значимых данных.

- Стоповый бит

- Последний бит в передаче одного байта через UART. Его логический уровень равен логическому уровню в состоянии ожидания, то есть, логической единице. Это еще один вспомогательный бит.

Стартовый и стоповый биты в передаче байта через UART - Битовая скорость

- Приблизительная скорость (в битах в секунду, или бит/с, bps), с которой данные могут быть переданы. Более точное определение частоты (в бит/с) соответствует времени (в секундах), необходимому для передачи одного бита цифровых данных. Например, для системы 9600 бит/с, для передачи одного бита требуется 1/(9600 бит/с) ≈ 104,2 мкс. Эта система не может на самом деле передавать 9600 бит значимых данных в секунду, так как требуется дополнительное время для передачи служебных битов и, возможно, для задержек между передачами отдельных байтов.

Битовая скорость и время передачи одного бита через UART - Бит четности

- Бит обнаружения ошибок, добавленный к концу байта. Возможны два типа: «нечетность» означает, что бит четности будет равен логической 1, если байт данных содержит четное количество битов, равных логической 1, и «четность» означает, что бит четности будет равен логической 1, если байт данных содержит нечетное количество битов, равных логической 1. Это может показаться нелогичным, но идея состоит в том, что бит четности гарантирует, что количество битов, равных логической 1, всегда будет нечетным (для нечетности) или четным (для четности). Поэтому, если вы используете четность, и байт имеет три бита, равных логической 1, то общее количество битов, равных логической 1 в переданных данных, (то есть, сам байт плюс бит четности) будет четным.

Принудительно приводя количество битов, равных логической единице, к четному (при четности) или нечетному (при нечетности) количеству, бит четности обеспечивает грубый механизм обнаружения ошибок – если где-то в процессе передачи какой-либо бит будет перевернут, то количество битов, равных логической 1, не совпадет с выбранным режимом четности. Конечно, этот метод не поможет, если будут перевернуты значения сразу двух битов, поэтому бит четности не так уж и надежен. Если вам действительно нужна устойчивая к ошибкам связь, я бы рекомендовал использовать CRC.

Как работает UART

Передатчик и приемник используют стартовый бит, стоповый бит и параметры синхронизации для взаимодействия друг с другом. Исходные данные находятся в параллельной форме. Например есть 4-х битные данные, и чтобы преобразовать их в последовательную форму нужен преобразователь из параллельного в последовательный. Обычно для проектирования преобразователей используются D-триггеры.

D-триггер, также известный как триггер данных, сдвигает один бит со стороны входа на сторону выхода только тогда, когда таймер изменяет переход из высокого состояния в низкое или из низкого состояния в высокое. Точно так же, если надо передать 4 бита данных, понадобится 4 триггера.

- D — входные данные.

- CLK — тактовые импульсы.

- Q — выходные данные.

Теперь спроектируем преобразователь из параллельного в последовательный и из последовательного в параллельный.