4.4. Триггеры

Триггер

– это устройство с двумя устойчивыми состояниями, одно из которых – логический нуль, другое – логическая единица. Эти состояния триггера при бесперебойном питании и при отсутствии существенных помех и наводок могут сохраняться сколь угодно долго. Под действием управляющих сигналов триггер способен переключаться из одного состояния в другое. Основноеназначение триггера – хранение двоичной информации. Например, в персональных компьютерах на триггерах собрана кэш-память первого и второго уровней.

Триггер, в отличие от комбинационных схем, относится к новому виду цифровых устройств – цифровым автоматам

. Цифровые автоматы, кроме комбинационных схем, содержат элементы памяти. Если выходные сигналы цифрового автомата зависят как от входных сигналов, так и от состояния запоминающего устройства, то такие автоматы называют автоматами Мили. Если выходные сигналы определяются только состояниями запоминающего устройства, то получим автомат Мура.

Различают несколько разновидностей триггеров: RS

-триггер,D -триггер,JK -триггер. Реже используютсяDV -триггер иТ -триггер. Если для изменения состояния триггера используется синхронизирующий сигнал, то триггер называетсясинхронным (синхронизируемым). Если синхронизирующие сигналы не используются, то триггер называетсяасинхронным .

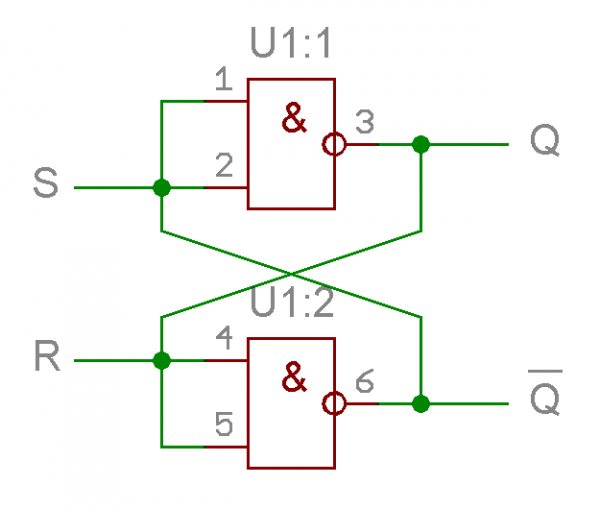

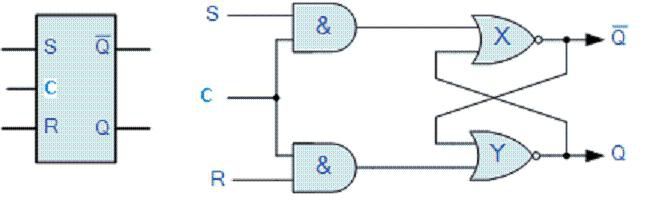

Например, в простейшем асинхронном RS- триггере

использованы схемы ИЛИ-НЕ (стрелка Пирса) с перекрестными обратными связями (рис. 4.21). Здесь использованы следующие обозначения:R – вход установки триггера в 0;S – вход установки триггера в 1;Q – прямой выход триггера; – вспомогательный (инверсный) выход триггера, сигнал на котором инвертирован относительно прямого выхода. Такие же обозначения используются для наименованиясигналов на соответствующих контактах триггера.

Рассмотрим работу RS

-триггера. Пусть в нулевой момент времени при нулевых сигналах на входахR иS на триггер подано напряжение питания. Однако на выходах триггера в этот момент времени оба выходных сигнала будут равны нулю:

Мгновенно эти сигналы увеличиться не могут, так как в реальных схемах всегда имеются паразитные емкости, а напряжение на конденсаторе скачкообразно измениться не может. Из свойств элемента ИЛИ-НЕ следует, что при нулевых сигналах на его входах напряжение на его выходе должно возрастать до значения логической единицы.

На практике из-за не идентичности двух элементов ИЛИ-НЕ на одном из выходов (Q или ) напряжение возрастает быстрее.

Пусть более быстро напряжение возрастает на выходе Q. Это напряжение поступает на второй логический элемент и начинает уменьшать напряжение на его выходе , устремляя его к нулю. В свою очередь, уменьшающееся напряжение на выходе , попадая на первый логический элемент, еще более ускоряет увеличение напряжения на выходе Q. Таким образом, благодаря положительной обратной связи быстро устанавливается единичное состояние триггера:

Q =

1;= 0.

Подавая на вход R

логическую единицу приS = 0 и используя свойства схемы ИЛИ-НЕ, получим:

Q

= 0; = 1.

Так производится операция установки триггера в нулевое состояние. Если после этого сигнал на входе R

сделать равным 0, то новое состояние триггера сохраняется.

При подаче единицы на вход S

и приR = 0 триггер устанавливается в единичное состояние:

Q

= 1.

Если R =S = 1, то на обоих выходах,Q и , возникают нули, что противоречит определению выходов триггера. Такая комбинация управляющих сигналовзапрещена (после этого работоспо собность триггера не теряется). Таблица состоянийRS -триггера приведена на рис. 4.22.

При хранении состояние триггера в данный момент времени определяется его состоянием в предыдущий момент времени:

где n

– номер временного отсчета. Условное обозначениеRS -триггера приведено на рис. 4.23.

Рассмотренный RS-

триггер при наличии помех часто работает ненадежно. Например, короткие импульсные помехи, попадающие наR — илиS -входы, могут изменить состояние триггера. Для повышения помехоустойчивости и для устранения «состязаний» используютсинхронныйRS-триггер, схема и условное обозначение которого приведены на рис. 4.24,а,б соответственно.

Состояние синхронного триггера может измениться только при установлении логической единицы на входе синхронизации С. В этом случае элементы И «открываются», и управляющие сигналы поступают на входы асинхронного триггера. Такая синхронизация называется статической

.

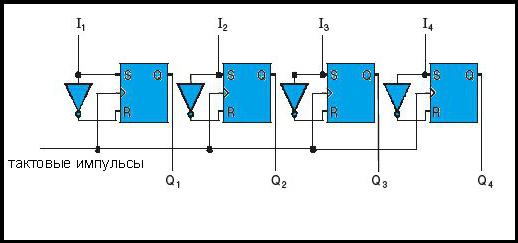

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

Схема 4-х разрядного регистра сдвига на триггерах

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.

Значение слова триггер

(англ. trigger), спусковое устройство ( спусковая схема ), которое может сколь угодно долго находиться в одном из двух (реже многих) состояний устойчивого равновесия и скачкообразно переключаться из одного состояния в другое под действием внешнего сигнала. Т. имеет два выхода: основной и инверсный. Каждому состоянию Т. соответствуют определённые сигналы на его выходах, отличающиеся своим уровнем. В одном состоянии на основном выходе Т. формируется сигнал высокого уровня, а на инверсном ≈ низкого; в др. состоянии, наоборот, сигналы высокого и низкого уровней формируются соответственно на инверсном и основном выходах. Т. характеризуется следующими важнейшими параметрами: быстродействием, временем срабатывания, уровнями входных и выходных сигналов. Быстродействие Т. определяется как максимальное возможное число переключений в единицу времени. Время срабатывания определяется временем перехода Т. из одного состояния в другое и характеризует задержку выходного сигнала Т. относительно входного. Под уровнем входного сигнала понимают минимальное значение сигнала, необходимое для переключения Т. Уровень выходного сигнала у большинства Т. не ниже уровня входного сигнала, чем обеспечивается возможность их последовательного соединения без промежуточного усиления.

Наибольшее распространение получили электронные Т., выполненные на электронных лампах, газоразрядных приборах, полупроводниковых диодах, транзисторах разных типов и особенно на интегральных микросхемах; иногда применяются также Т. на магнитных элементах, элементах пневмо- и гидроавтоматики и др. По характеру входных сигналов различают Т. с потенциальными входами (прямым и инверсным) и динамическими входами (также прямым и инверсным). Т. с потенциальными входами реагируют на сигнал высокого уровня на прямом входе и низкого уровня на инверсном входе. Т. с динамическими входами реагируют на перепады (изменения уровня) входных сигналов: положительный на прямом входе и отрицательный на инверсном.

══Наиболее часто применяют: Т. со счётным входом (Т-триггер), который изменяет своё состояние на противоположное с каждым входным сигналом; Т. с двумя установочными входами (R ≈ S-триггер), изменяющий своё состояние только при воздействии управляющего сигнала на определённый вход (R-или S-вход), причём повторное воздействие сигнала на тот же вход Т. не изменяет его состояния; универсальный Т. (J ≈ K-триггер), обладающий свойствами Т-триггера и R ≈ S-триггера; Т. задержки (D-триггер), состояние которого и соответствующий ему выходной сигнал повторяют входной сигнал. Кроме Т. этих типов, применяют комбинированные Т., представляющие собой универсальные многофункциональные устройства с большим числом входов.

Указанные выше Т. относят к симметричным; применяют также несимметричные Т. (Т. Шмитта). Несимметричный Т. переходит из одного состояния в другое по достижении входным сигналом одного уровня (порога срабатывания), а в исходное состояние возвращается при уменьшении входного сигнала до некоторого др. уровня. Существуют и многостабильные Т., обладающие числом устойчивых состояний, большим, чем два.

Т. различных типов применяют в устройствах цифровой вычислительной техники и автоматики. С использованием Т. строятся цифровые автоматы с программным управлением для дискретной обработки информации (в частности, счётчики, пересчётные устройства, регистры разных типов, дешифраторы, сумматоры и др.), формирователи импульсов, цифровые делители частоты и т.д. В цифровой автоматике Т. выполняют функции элементарных автоматов с памятью, имеющих 2 состояния, которым соответствуют два возможных значения двоичной логической переменной (х = 0 и х = 1). Такие Т. подразделяются на асинхронные и синхронные. Синхронные (тактируемые) Т. выполняют свои функции только при воздействии на их входы периодических тактовых сигналов (обычно меандрового типа), синхронизирующих работу Т. Синхронные Т. подразделяются на однотактные и двухтактные. Последние представляют собой систему из двух Т., выполняющих одну и ту же логическую операцию, но со сдвигом во времени на длительность полутакта входного тактового сигнала. Удвоение действий Т. необходимо для разделения во времени приёма информации, доставляемой входными сигналами, и передачи информации с выходов Т. на др. элементы устройства (или на его вход).

Лит.: Ицхоки Я. С., Овчинников Н. И., Импульсные и цифровые устройства, М., 1972; Старостин А. Н., Импульсная техника, М., 1973; Каган Б. М., Каневский М. М., Цифровые вычислительные машины и системы, М., 1973.

Ю. Б. Барабанов, И. А. Данильченко,

Е. И. Петровичев.

Что такое RS триггер

Хлопковый выключатель и его особенности

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

RS триггер

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние

Триггер RS типа

Одной из простейших в цифровой электронике является схема RS-триггера на транзисторах. Внешним воздействием на вход прибора можно установить его выход в нужное устойчивое состояние. Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного. Два состояния определяются присутствием на выходе напряжения, а переход между ними происходит с помощью управляющих сигналов.

Вам это будет интересно Особенности единицы измерения мощности вольт-ампер

Работает схема следующим образом. Если в начальный момент времени VT2 будет закрыт, тогда через сопротивление R3 и коллектор будет течь ток, поддерживающий VT1 в режиме насыщения. Одновременно первый транзистор начнёт шунтировать базу VT2 и резистор R4. Режим отсечки VT2 соответствует значению логической единицы на выходе Q = 1, открытое состояние VT1 нулю, Q = 0. Амплитуда сигнала на коллекторе закрытого ключа определяется выражением: Uз = U * R3 / (R2+R3).

Для инверсии сигнала необходимо на вход R или S подать импульс. При этом если S = 1, то и Q = 1, а если R=1, то на выходе будет ноль. При значениях R1 = R2 и R3 = R4 триггер называется симметричным. Особенностью работы устройства является способность удерживать установленное состояние между импульсами R и S, что и используется для создания на нём элементов памяти.

На схемах RS-триггер обозначается в виде прямоугольника с подписанными входами S и R, а также возможными состояниями выхода. Прямой подписывается символом Q, а инверсный – Q. Информация может поступать на входы непрерывным потоком или только при появлении синхроимпульса. В первом случае устройство называют асинхронным, а во втором – синхронным (трактируемым).

Работа устройства наглядно описывается с помощью таблицы истинности.

Она наглядно показывает всевозможные комбинации, которые могут возникнуть на выходе прибора. Такая таблица составляется отдельно для триггера с прямыми входами и инверсными. В первом случае действующий сигнал равен единице, а во втором — нулю.

Что такое RS триггер

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние

- 1 RS — триггер

- 1.1 Классическая реализация RS-триггера

- 1.2 Временные диаграммы RS-триггера

- 1.3 Другая реализация RS-триггера

- 2 Синхронный RS-триггер

- 3 Синхронный JK-триггер

- 3.1 Схема JK-триггера

- 3.2 Конкретная реализация синхронного JK-триггера

- 4 D-триггер

- 5 Т-триггер

- 6 Двухступенчатые триггеры

- 6.1 Двухступенчатый синхронный RS-триггер

- 6.2 Двухступенчатый D-триггер

- 6.3 Двухступенчатый JK-триггер

- 7 Универсальные триггеры

- 8 Ступенчатый D-триггер

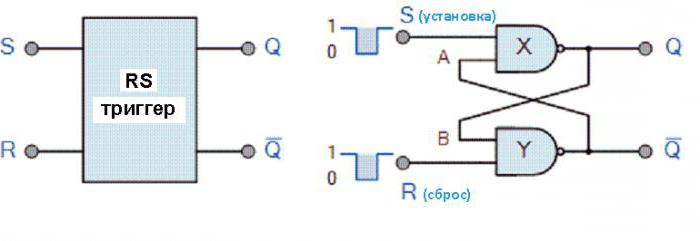

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

RS-триггеры

Логические устройства вычислительной техники

Что же такое RS-триггеры? В моем понимании — это устройства, которые могут принимать одно из двух состояний. На основании этого можно сделать вывод, что этот логический элемент может хранить один бит информации (грубо говоря, ноль или единицу). Существуют некоторые типы данного вида RS-триггеров. Давайте рассмотрим один из них:

Асинхронный RS-триггер

Имеет два входа “R» и «S” и два выхода, как правило это “Q” и “не Q” (т.е. инверсный) . Лично я запомнил, какой элемент для чего, после того, когда узнал, что R – это “RESET” (что означает “сброс”) и “S” – это “SET” (что означает установка)

Принимая во внимание изложенную информацию можно указать, что при подаче сигнала (единица) на “S” на выходе “Q” устанавливается единица, а при подаче единицы на “R” приводит к сбросу единицы на выходе “Q” и установки на нем нуля. Рассмотрим работу на базе элементов “2ИЛИ-НЕ” и “2И-НЕ”

Для этого используем графическое изображение этих элементов.

Итак, разберем принцип работы RS-триггера на базе элементов “2ИЛИ-НЕ”. В начальном положении, когда на R и S отсутствуют сигналы (логический “0”), на выходе “Q” присутствует также “0” или “1” – это исходное состояние. Выглядит это так:

Далее подадим на “S” логическуюединицу и получим на выходе “Q” также единицу. Будет выглядеть это так.

Следующим шагом подадим логическую единицу на “R” и уже на “Q” получим “0”. Изобразим это на рисунке.

Более наглядную работу RS-триггера на элементах 2ИЛИ-НЕ можно продемонстрировать, изобразив таблицу истинности. Вот так она выглядит.

Сейчас рассмотрим работу на элементах 2И-НЕ. Выглядит она аналогично, как и на элементах 2ИЛИ-НЕ с той лишь разницей, что активным уровнем является не “1”как в предыдущем случае, а “0”. Убедимся в этом, используя рисунок и таблицу истинности.

Асинхронным триггерам свойственно такое явление как присутствие “гонок”, что это? Это не одновременное или даже не согласованное по времени поступление информации на входы. Это приводит к наложению одного сигнала на другой. Чем это вызвано? А вызвано это разным временем быстродействия элементов, через которые проходит сигнал, прежде чем попасть на входы триггера, в данном случае на “R” или “S”. Покажем это явление на диаграмме.

Чтобы избавиться от этого явления, был придуман вариант подачи синхросигнала и асинхронный триггер превратился в синхронный.

Синхронные RS–триггеры

Этот вид логического устройства отличается от рассмотренного выше тем, что у него помимо входов “R” и “S” присутствует и третий “C”, на который подаются синхроимпульсы. Без этих импульсов информация на “R” и ”S” восприниматься не будет. Схему синхронного RS–триггера и диаграмму работы изобразим графически.

Из диаграммы видно, что в данном случае срабатывание происходит по переднему фронту (но бывает и по спаду) синхроимпульса.

Передний фронт синхроимпульса – это участок прямоугольного импульса, где происходит его возрастание.

Спад синхроимпульса – это участок спада синхроимпульса.

Именно здесь сделаем небольшое отступление и укажем, что бывают триггеры динамические и статические и соответственно со статическим и динамическим управлением. Чем они отличаются? Объясним максимально просто.

Динамические триггеры – на выходах, которых присутствуют либо непрерывная последовательность импульсов определенной частоты, либо ее отсутствие. (Напоминает управляемый генератор).

Статические триггеры– на выходах которых присутствуют неизменный уровень напряжения, либо его отсутствие.

Со статическим управлением – восприятие сигналов на информационных входах происходит только при подаче на “С” логической единицы (логического нуля).

С динамическим управлением – восприятие сигналов на информационных входах происходят в моменты перепада сигнала на “С”(Передний фронт синхроимпульса или спад синхроимпульса).

Если логические функции входов зависят от его выходов, то целесообразно использовать более рациональную конструкцию элементов.

Как синхронизировать работу триггера

Иногда желательно в последовательностных логических схемах иметь бистабильный триггер, изменяющий свое состояние, когда соблюдены определенные условия, независимо от состояния S- или R-входов. Такая схема может быть создана подключением двухвходного элемента И последовательно с каждого входом триггера. Объединив два входа элементов И, получим новый вход триггера. Добавление его означает, что выходы Q и Q̃ изменяют состояние, когда сигнал на нем является высоким, и, следовательно, он может быть использован в качестве тактового C-ввода, как показано на рисунке ниже.

Когда сигнал на С-входе находится на уровне 0, то выходы двух элементов И — также на уровне 0 (логика элемента И), независимо от состояния двух входов S и R, а два выхода Q и Q̃ «защелкнуты» в последнем установившемся состоянии. Когда сигнал на С-входе изменяется на уровень 1, то схема отвечает как обычный бистабильный триггер, становясь прозрачной для установки и сброса состояний.

Этот дополнительный C-вход также может быть подключен к выходу генератора тактовой частоты синхронизации, образуя тогда синхронный RS-триггер. Таким образом, данная схема работает как стандартная бистабильная триггерная «защелка», но выходы активируются только тогда, когда уровень 1 подан на C-вход, и отключаются при появлении уровня логического нуля.

RS-триггер на логических элементах

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

Триггеры

Результаты операций, как и сами операнды, надо где-то как-то хранить. Для этого используются логические элементы, известные как триггеры.

- Триггер

- Логический элемент, способный хранить один разряд двоичного числа.

RS-триггер

Представляет собой простейший триггер. Имеет следующую схему:

RSQQ

По сути, состоит из двух элементов ИЛИ-НЕ, соединенных кольцом.

Имеет следующую таблицу истинности:

| R | S | Q |

|---|---|---|

| Q | ||

| 1 | 1 | |

| 1 | ||

| 1 | 1 | ? |

При подаче нулей на оба входа, хранится ранее установленное значение. При подаче 1 на вход S (Set), значение устанавливается в 1, при подаче 1 на вход R (Reset), значение сбрасывается в 0.

Подавать 1 на оба входа одновременно запрещено, поскольку в таком случае \(Q=\;\overline{Q}\; = 0\). При подаче после этого нулей на оба входа, состояние триггера не определено (зависит от внутренних характеристик элементов)

Регистры на триггерах

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.