Утилиты (Портативные) » Logisim 2.7.1 Portable ML/Rus

Logisim — свободное программное обеспечение, выпущенное под GNU GPL, позволяющее разрабатывать и моделировать цифровые электрические схемы, используя графический интерфейс пользователя. Может запускаться на Microsoft Windows, Mac OS X и Linux. Код полностью написан на Java с использованием библиотеки Swing для графического интерфейса пользователя.

Программа чаще всего используется учащимися в курсе изучения информатики для разработки и экспериментов с цифровыми схемами при моделировании. Схемы разрабатываются в Logisim с помощью графического интерфейса, близкого к традиционному для программ для рисования, такой интерфейс встречается во многих других программах для моделирования схем. В отличие от большинства других программ такого назначения, сопоставимых с Logisim по сложности, Logisim позволяет пользователям редактировать схемы в процессе моделирования. Относительная простота интерфейса делает программу удобной для обзорных курсов. Возможности разработки более сложных схем, такие как «подсхемы» и «пучки проводов», имеющиеся в Logisim, доступны в некоторых других графических инструментах с открытым исходным кодом.Хотя пользователи могут разрабатывать даже полные реализации процессоров, используя Logisim, программа разработана в основном для образовательного использования. Профессионалы обычно разрабатывают такие масштабные схемы, используя языки описания аппаратуры, такие как Verilog или VHDL. Logisim не позволяет работать с аналоговыми компонентами.Особенности* Это бесплатно! Logisim с открытым исходным кодом (GPL).* Она работает на любой машине, поддерживающих Java 5 или более поздние версии; специальные версии выпущены для MacOS X и Windows

Кросс-платформенность имеет важное значение для студентов, которые имеют различные компьютерные системы.* Иинтерфейс основан на интуитивной панели инструментов. Цветовая маркировка проводов помогает в моделировании и отладке схем.* Программа рисует горизонтальные и вертикальные проводники, автоматическое подключение к компонентам и к другим проводникам

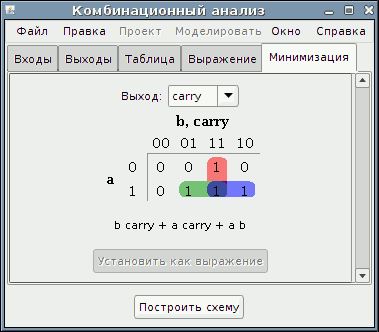

Это помогает легко делать схемы!* Завершенные схемы могут быть сохранены в файл, экспортированы в файл GIF или распечатаны на принтере.* Автоматические макеты могут быть использованы в качестве «подсхем» других схем, позволяя создавать иерархические схемы.* Элементы схем включают входы и выходы, логические элементы, мультиплексоры, компоненты ОЗУ и ПЗУ, ….* Включен модуль «Комбинационный анализ», позволяющий преобразовывать данные между логическими схемами, логическими выражениями и таблицой истинности. Комбинационный анализ позволяет вам конвертировать данные между этими тремя представлениями во всех направлениях* Не требует установки — один исполняемый файл.’);if(«undefined»===typeof loaded_blocks_da){loaded_blocks_da=[];function n(){var e=loaded_blocks_da.shift();var t=e.adp_id;var r=e.div;var i=document.createElement(«script»);i.type=»text/javascript»;i.async=true;i.charset=»utf-8″;i.src=»https://code.directadvert.ru/show.cgi?async=1&adp=»+t+»&div=»+r+»&t=»+Math.random();var s=document.getElementsByTagName(«head»)||document.getElementsByTagName(«body»);s.appendChild(i);var o=setInterval(function(){if(document.getElementById(r).innerHTML&&loaded_blocks_da.length){n();clearInterval(o)}},50)}setTimeout(n)}loaded_blocks_da.push({adp_id:e,div:t})})(233229)Logisim распространяется с поддержкой русского интерфейса и полной документацией на русском языке.

The latest version 2.7.1 of March 21, 2011Platforms: Windows Multilingual user interface (English, Russian, etc)Licence: FreewareDeveloper: ozark.hendrix.eduSize: 6.64 Mb

Download Deposit

Download Turbobit

Download Rusfolder

- Просмотров: 3283 |

The Compiler

The compiler is a way to convert the above Assembly code into machine code. Since the CPU is developed in Logisim, the file format chosen was the file format that allows reading and writing to the built in RAM modules. Below is a sample program that adds the values and (Decimal and ) and stores the value in memory address 0, halting with exit code 0.

This compiler is written in python, due to its flexibility and lightweight code (the full compiler, with warnings and system argument parsing is still less than 2KB, less than the cluster size on MacOS and some other operating systems). Relative to the size of the programs this compiler is working on, the file size is daunting, being 4 times the size, but if the CPU were able to handle more information, by moving from 4 to 8 or even 16 bits, the compiler would only increase enough to accommodate any new commands.

The CPU

The CPU I’ve designed is by no means the most efficient design, but its purpose isn’t to be the most efficient or the fastest, but rather as a learning experience. The design is not the same as most low-powered CPUs, as there are separate memory banks for the instructions and the usable memory. There is functionality to manipulate the contents of the instruction bank, but that is purely to alter the course of the program. Each 8-bit memory bank can hold 256 bytes of information, leading to a maximum program size of 256 bytes, and a total of 256 bytes of usable memory. There are various registers in the CPU that can each hold a small amount of information. Registers A and B can each hold a byte of information, the Memory Address Register can hold half a byte (a nibble) of information, and the Carry On Operation Register can hold a measely 1 bit of information. Combining these memory registers, there is a total of 514.625 bytes (4117 bits) of information stored at any given moment, 258 bytes being usable between the memory bank, and two main registers.

Продвинутые и редко используемые логические символы

Эти символы отсортированы по их значению Unicode:

-

U + 0305 ̅ ОБЪЕДИНЕНИЕ СТРОКИ , используется как сокращение для стандартных цифр ( теория типографских чисел ). Например, использование стиля HTML «4̅» является сокращением для стандартной цифры «SSSS0».

- Overline также является редко используемым форматом для обозначения чисел Гёделя : например, « A ∨ B » означает число Гёделя «(A ∨ B)».

- Overline также является способом обозначения отрицания, используемого в основном в электронике: например, « A ∨ B » то же самое, что и «¬ (A ∨ B)».

- U + 2191 ↑ СТРЕЛКА ВВЕРХ или U + 007C | ВЕРТИКАЛЬНАЯ ЛИНИЯ : штрих Шеффера , знак оператора И-НЕ (отрицание соединения).

- U + 2193 ↓ СТРЕЛКА ВНИЗ Стрелка Пирса , знак оператора ИЛИ (отрицание дизъюнкции).

- U + 2299 ⊙ CIRCLED DOT OPERATOR знак для оператора XNOR (отрицание исключительной дизъюнкции).

- U + 2201 ∁ COMPLEMENT

- U + 2204 ∄ ТАМ НЕ СУЩЕСТВУЕТ : зачеркнуть экзистенциальный квантор, то же, что и «¬∃»

- U + 2234 ∴ ПОЭТОМУ : Поэтому

- U + 2235 ∵ : потому что

- U + 22A7 ⊧ МОДЕЛИ : это модель (или «удовлетворительная оценка «)

- U + 22A8 ⊨ ИСТИНА : верно для

- U + 22AC ⊬ НЕ ДОКАЗЫВАЕТСЯ : отрицание ⊢, знак «не доказывает», например, T ⊬ P говорит: « P не является теоремой для T »

- U + 22AD ⊭ НЕ ИСТИНА : неверно

- U + 2020 † DAGGER : Оператор подтверждения (читай: «это правда, что …»)

- U + 22BC ⊼ NAND : оператор NAND.

- U + 22BD ⊽ NOR : оператор NOR.

- U + 25C7 ◇ БЕЛЫЙ АЛМАЗ : модальный оператор для «возможно, что», «это не обязательно не обязательно» или редко «это, вероятно, не так» (в большинстве модальных логик он определяется как «¬¬»)

- U + 22C6 ⋆ СТАР ОПЕРАТОР : обычно используются для Времнных операторов

- U + 22A5 ⊥ ВВЕРХ или U + 2193 ↓ СТРЕЛКА ВНИЗ : оператор Уэбба или стрелка Пирса, знак для NOR . Как ни странно, «⊥» также является знаком противоречия или абсурда.

- U + 2310 ⌐ ПЕРЕВЕРНУТЫЙ НЕ ЗНАК

- U + 231C ⌜ ВЕРХНИЙ ЛЕВЫЙ УГОЛ и U + 231D ⌝ ВЕРХНИЙ ПРАВЫЙ УГОЛ : угловые кавычки, также называемые «кавычками Куайна»; для квази-цитирования, т. е. цитирования определенного контекста неопределенных («переменных») выражений; также используется для обозначения числа Гёделя ; например, «⌜G⌝» обозначает гёделевское число G. (Типографское примечание: хотя кавычки отображаются как «пара» в Юникоде (231C и 231D), они не симметричны в некоторых шрифтах. И в некоторых шрифтах (например, Arial) они симметричны только в определенных размерах. В качестве альтернативы кавычки могут быть представлены как ⌈ и ⌉ (U + 2308 и U + 2309) или с использованием символа отрицания и символа обратного отрицания ⌐ ¬ в режиме надстрочного индекса.)

- U + 25FB WHITE MEDIUM SQUARE или U + 25A1 □ WHITE SQUARE : модальный оператор для «необходимо, что» (в модальной логике ), или «это доказуемо» (в логике доказуемости ), или «это обязательно, что» (в деонтической логике ) или «считается, что» (в доксастической логике ); также как (альтернативы:и ⊥).∅{\ displaystyle \ emptyset}

- U + 27DB ⟛ LEFT AND RIGHT TACK : семантический эквивалент

Следующие операторы редко поддерживаются изначально установленными шрифтами.

- U + 27E1 ⟡ БЕЛЫЙ Вогнутый алмаз : модальный оператор никогда

- U + 27E2 ⟢ БЕЛЫЙ Вогнутый бриллиант с левой галочкой : модальный оператор для никогда не был

- U + 27E3 ⟣ БЕЛЫЙ Вогнутый бриллиант с галочкой вправо : модальный оператор for никогда не будет

- U + 25A1 □ WHITE SQUARE : модальный оператор для Always

- U + 27E4 ⟤ БЕЛЫЙ КВАДРАТ С ЛЕВОЙ КАРТИНКОЙ : модальный оператор для всегда был

- U + 27E5 ⟥ БЕЛЫЙ КВАДРАТ С ТИПОМ ВПРАВО : модальный оператор для всегда будет

- U + 297D ⥽ ПРАВЫЙ

- U + 2A07 ⨇ ДВА ЛОГИКА И ОПЕРАТОРА

Поведение

Контакт — это выход или вход схемы, в зависимости от значения атрибута Выход? . При отрисовке контакта Logisim представляет выходные контакты как кружки или скруглённые прямоугольники, а входные контакты как квадраты или прямоугольники. В обоих случаях отдельные биты значения, которое оправляется или принимается, отображаются внутри данного компонента (кроме Вида для печати, когда компонент говорит только какова разрядность контакта).

Контакт — удобный компонент для взаимодействия со схемой, и начинающим пользователям Logisim не нужно использовать их каким-либо другим образом. Но пользователь, строящий схему с использованием нескольких подсхем (как описано в разделе «Подсхемы» Руководства пользователя ) будет использовать контакты также чтобы определить интерфейс между схемой и подсхемой. В частности, компоненты Контакт чертежа схемы определяют контакты, которые отображаются на компоненте Подсхема, когда чертёж используется внутри другой схемы. В такой схеме значения, переданные и принятые в этих точках компонента Подсхема, связаны с контактами внутри чертежа подсхемы.

Контакты

* Звёздочкой отмечены контакты, существующие только когда атрибут Параллельная загрузка включен.

- Западный край, верхний контакт (вход, разрядность равна 1)

- Сдвиг: когда на нём 1 или он не подключен, все ступени сдвигаются при срабатывании тактового входа; но если на нём 0, никакого сдвига не происходит. Этот вход игнорируется, если на входе Загрузка 1.

- Западный край, средний контакт (вход, разрядность соответствует атрибуту Биты данных)

- Данные: при продвижении ступеней значение с этого входа загружается в первую ступень.

- Западный край, нижний контакт, отмечен треугольником (вход, разрядность равна 1)

- Тактовый вход: в момент срабатывания этого входа, как указано в атрибуте Срабатывание, компонент может сдвинуть ступени или загрузить новые значения.

- *Северный край, левый контакт (вход, разрядность равна 1)

- Загрузка: когда на этом входе 1, значения с остальных контактов на северном крае загружаются во все ступени при следующем срабатывании тактового входа. Когда на нём 0 или он не подключен, никакой загрузки не происходит.

- *Северный край, остальные контакты (вход, разрядность соответствует атрибуту Биты данных)

- Данные: эти значения загружаются во все ступени при срабатывании тактового входа, пока на входе Загрузка 1. Крайний левый вход соответствует младшей ступени.

- Южный край, левый контакт (вход, разрядность равна 1)

- Очистка: когда значение равно 1, все ступени асинхронно сбрасываются на 0, и все другие входы игнорируются.

- *Южный край, остальные контакты (выход, разрядность соответствует атрибуту Биты данных)

- Выход: выдаёт значение, хранящееся в каждой ступени; младшая ступень отражена в крайнем левом контакте (рядом со входом Очистка).

- Восточный край (выход, разрядность соответствует атрибуту Биты данных)

- Выход: выдаёт значение, хранящееся в последней (старшей) ступени.

Libraries

This section contains libraries of components that can be

imported into Logisim. If you have your own library of

components that you think would be useful to others, I’ll be

happy to post a link here to a hosting Web site or to the

library itself.

-

7400 series Logisim

library from Ben Oztalay (ZIP,

uncompressed) -

A set of Logisim circuits corresponding to a large number of

7400-series chips, produced by Ben Oztalay. The pin layout

matches the 7400 IC layouts.

(2011, released into public domain). -

7400 series Logisim

library from Technological Services Company (ZIP,

uncompressed) -

A set of Logisim circuits corresponding to a large number of

7400-series chips, produced by Technological Services Company.

The pin layout has inputs on the left, outputs on the right.

(Copyright 2005, released under the GPL). - Gray Counter example (JAR)

- The JAR library described in the Logisim

User’s Guide for version 2.3.0 and later. - Incrementer example (JAR)

- The outdated JAR library described in the Logisim

User’s Guide prior to version 2.3.0. Compatible with

versions Logisim 2.0 Beta 20 and later. The class name is

com.cburch.incr.Components.

Schools using Logisim

This is a very incomplete list. Logisim does not demand that

downloaders fill a form saying why they are downloading it;

instead, we rely entirely on volunteers to report their usage.

View schools using Logisim

in a larger map

| Argentina | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad Catolica Argentina — Rosario |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad Nacional del Centro de la Provincia de Buenos Aires |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad Nacional del Sur |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Australia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Bond University | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Curtin International College | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| University of Newcastle | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| University of Queensland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Austria | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Graz University of Technology | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Bangladesh | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| North South University | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Belgium | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Ecole Supérieure d’Informatique — Haute Ecole de Bruxelles |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Antwerp | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Mons | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Université Libre de Bruxelles | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Brazil | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Sao Paulo | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidade Federal de Mato Grosso do Sul | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PUC Minas | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Bulgaria | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| American U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Technical U — Sofia, Plovdiv branch | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Canada | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Augustana U, Alberta | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Camosun C | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| McGill U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mount Royal U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mohawk C of Applied Arts and Tech | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of British Columbia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Chile | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Chile | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| China | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Putian U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Croatia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Zagreb Polytechnic | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Colombia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad Pontificia Bolivariana, Medellin | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad del Norte | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad EAFIT — Medellin | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| I Pedro Luis Villa | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Cyprus | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| European University Cyprus | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Czech Republic | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Inst of Chemical Technology, Prague | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Denmark | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Copenhagen | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Finland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Joensuu | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| France | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Supélec | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Nantes | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Rennes | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U Inst of Tech, Grenoble | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Germany | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Duisburg-Essen | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Siegen | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Greece | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Peloponnese | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Tech Educ Inst of Ionian Islands | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Iceland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Iceland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| India | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Holy Cross Matriculation Higher Secondary School | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Indian Inst of Tech, Dehli | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Lebanon | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| American U of Beirut | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mexico | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidad Autnoma de Baja California, Tijuana | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| New Zealand | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Auckland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Victoria U of Wellington | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Waikato | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Portugal | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Universidade de Évora | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Russia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Moscow University of Printing Arts | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Saudia Arabia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| King Fahd University of Petroleum and Minerals | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Serbia | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Niš | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Singapore | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| National U of Singapore | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Sweden | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Nordiska Tekniska Institutet | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Uppsala U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Switzerland | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Ecole Polytechnique Federale de Lausanne | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Haute école spécialisée de Suisse occidentale | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Lugano | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Taiwan | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| National Chi Nan U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Turkey | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Bartin U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Karabuk U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Koc University | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Middle East Technical U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| United Kingdom | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Oxford & Cherwell Valley C | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Oxford Brookes U | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| U of Sheffield | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| United States of America | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Above, I have tried to list only those institutions where I

feel there is firm information that Logisim has been assigned directly

for use by students. Not included are courses that recommend Logisim

without making explicit assignments nor those who offer a choice

between Logisim and another piece of software. (Also, for those found

through Web searches, I look for specific evidence that the software

package is not an obscure competitor that happens to share Logisim’s

name.)

Familiarizing yourself with the Logisim software interface

After downloading and installing the Logisim software, you will need to first familiarize yourself with its graphical user interface before you can use it without any difficulty. In this article, I will give a very brief overview of the graphical user interface of the Logisim software. However, I would suggest that you read through the documentation of the Logisim software (which can be found here: http://www.cburch.com/logisim/docs.html), to give you more knowledge on how to navigate through the software.

The user interface of the Logisim software

Fig. 1 below depicts the various parts of a typical Logisim software interface.

Fig. 1

– The Menu Bar: contains the various instructions that can be executed in the Logisim software.

– The Toolbar: contains shortcuts to the most commonly used commands in the Logisim software. The table in Fig. 2 below depicts the various commands on the Toolbar and their functions.

Fig. 2

– The Explorer Pane: contains a list of digital circuit components (such as wiring, gates, multiplexers, etc.) that are available for digital circuit design in Logisim.

– The Attribute Table: gives detailed attributes of digital design components (e.g. AND, OR and XOR gates). It also enables the attributes of these digital design components to be edited.

– The Canvas: the area in which digital circuits are created and designed. The Canvas enables digital circuits to be designed and simulated simultaneously.

Вкладка Минимизация

Последняя вкладка отображает минимизированное выражение суммы произведений, соответствующее столбцу таблицы истинности. Вы можете выбрать, для какого выхода вы хотите просматривать минимизированное выражение с помощью списка наверху.

Если входов четыре или меньше, то ниже списка появится карта Карно, соответствующая выходной переменной. Вы можете щёлкать на карте Карно для изменения соответствующих значений таблицы истинности. Карта Карно будет также показывать выбранные в данный момент для минимизированного выражения термы в виде сплошных полупрозрачных скругленных прямоугольников.

Ниже — само минимизированное выражение, отформатированное так же, как во вкладке Выражение. Если выходов более четырёх, то карта Карно не появится, но минимизированное выражение всё равно будет вычислено. (Logisim использует метод Куайна — Мак-Класки для вычисления минимизированного выражения. Он эквивалентен карте Карно, но применим к любому числу входных переменных.)

Кнопка Установить как выражение позволяет вам выбрать минимизированное выражение как выражение, соответствующее переменной. Это, как правило, не нужно, поскольку изменения в таблице истинности приводят к использованию минимизированного выражения для изменённого столбца; но если вы введете выражение через вкладку Выражение, то это может быть удобно, чтобы перейти к соответствующему минимизированному выражению.

Далее: Создание схемы.

Changelog

- Core Stuff:

- Italian, Simplified Chinese and partial french translation!

- Autoupdates!

- Compiled with Java 14

- Complete new movement system with mouse dragging

- Auto center and Auto zoom when opening new files/circuits or with ctrl-0, double mouse wheel click and with the round button you’ll see on the lower-right corner

- Almost infinite canvas, arrows will show you in what direction is the circuit if it’s outside of your view

- Zoom in and out using mouse wheel where you’re pointing at

- Double click with Edit Tool to label components

- Load libraries from folder at startup (Preferences / Fork)

- Selectable painting refresh rate, default 60Hz (Legacy was 20Hz and sometimes lagging)

- Anti Aliasing, Look and Feel and Fill Component’s Background preference

- Clock custom frequency

- Press ESC or DEL to cancel «Add Tool» action, F1 opens Library Reference

- Increased output limit in Analyze Circuit to 32

- Analyze Circuit should calculate table/expression with any kind of component

- Added «Clear Log» button

- Added missing tooltips

- Changed some default values

- New components:

- Wiring->Programmable Generator

- TTL gates (7400, 7402, 7404, 7408, 7432, 7447, 7485, 7486, 74165, 74283, 747266)

- I/O->Digital Oscilloscope

- I/O->Switch

- I/O->Dip Switch

- I/O->Slider

- I/O->RGB LED

- I/O->Buzzer

- Memory->PLA ROM

- Plexers->7-Segment Display Decoder

- Component changes:

- New FF layout

- The Shift Register will show you its internal bits even when set to serial load

- Right click on Pin, Edit Contents and set its value typing the decimal number

- Added Sel pin in Register

- Added Preset pin in Register and Counter

- TTY and Keyboard components can use 16-bit values (UTF-16)

- New Attributes:

- Controlled Buffer / Inverter: Negate Control Input attribute

- Added Sel Active Level attribute in components with Sel pin

- Priority Plexer «No Input» attribute

- Joystick «Facing» attribute

- Bit Selector «Select location» attribute

- Added Label Color attribute for each component with Label attribute and Text Tool

- Added Label for RAM, ROM and PLA ROM

- FF D, S-R: «Latch» option in Trigger attribute

- New Counter behavior (different pin logic)

- Fixed bugs:

- Big fixes to Log menu and Log output file

- Big fixes for Text Tool

- Fixed empty template bug introduced in Logisim 2.7.0

- Fixed input positions in wide gates with 4 inputs

- Fixed opening new file in new window with old window not used

- Fixed bugged 32b multiplier

- Some fix from original early version 2.7.2.255

Free graphical tools

My hope is that some day some other software developers out there

will create something that in my view renders Logisim irrelevant.

So I occasionally browse the competition

to see whether that day

has come. Here’s a list of links, and you can judge for yourself.

-

Digital

Works 2.0 is Windows freeware. It is a fairly complete

package, but it is no longer under development. I no longer know

where one can download a copy. 18 Jul 2007. -

HADES

is a Java-based tool, which is available at no cost but does not

appear to be open-source. The simulation and library functionality

is quite extensive, but the interface is on the awkward side.

18 Jul 2007 -

JLS

is a Java-based tool that is available at no cost from the author but

is not open-source or freeware. It doesn’t simulate circuits as you

build them, but its simulation capabilities are more extensive than

Logisim’s. 18 Jul 2007 -

Logisim is an open source Java tool.

Of course, I think it’s the best choice. 18 Jul 2007 -

MultiMedia

Logic is open source Windows software; It doesn’t seem to support

hierarchical circuits or wire bundling, so it’s quite limited as far

as designing CPU-scale circuits, but it does provide a fun set of

I/O components. 18 Jul 2007 -

TkGate is

open source software. It’s probably the most legitimate no-cost

competitor to Logisim: It’s simulation facilities seem quite sound,

though the interface strikes me as rather awkward. It requires tcl/tk

to run; it can run on Windows if you have Cygwin installed.

18 Jul 2007 -

xLogicCircuits

is my favorite among the bare-bones Java applets. It has some

utility if you’re spending one or two weeks introducing students to

the subject. 18 Jul 2007 - Other alternatives I have investigated, but which don’t yet seem

have much to recommend them:-

KLogic, open

source Linux - LogicSim, open source Java

- Digital Simulator, closed source shareware, free for education

-

KLogic, open

You might also find my more exhaustive outdated list useful. Maybe.

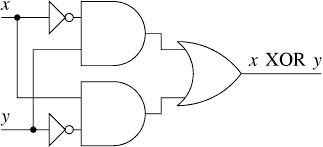

Шаг 1: Добавление логических элементов

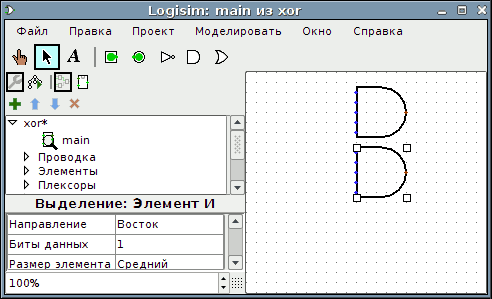

Вспомним, что мы пытаемся построить следующую схему в Logisim.

Я предлагаю строить схему, добавляя сначала элементы, как своего рода каркас, а потом соединять их проводами. Первое, что мы сделаем, это добавим два элемента И. Нажмите на инструмент Элемент И на панели инструментов (, предпоследний инструмент в списке). Затем щёлкните в области редактирования там, где вы хотите поместить первый элемент И. Не забудьте оставить достаточно места для вещей слева. Затем нажмите на инструмент Элемент И снова и поместите второй элемент И под первым.

Обратите внимание на пять точек на левой стороне элемента И. Это места, где могут быть прикреплены провода

Так получилось, что мы используем только два из них для нашей схемы Исключающее ИЛИ; но для других схем вы можете обнаружить, что более чем два провода, идущие к элементу И, могут быть полезны.

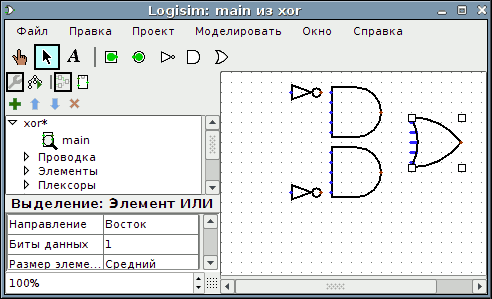

Теперь добавьте другие элементы. Сначала щёлкните на инструменте Элемент ИЛИ (); затем щёлкните там, где вы хотите его поместить. И расположите два элемента НЕ на холсте, используя инструмент Элемент НЕ ().

Я оставил немного пространства между элементами НЕ и элементами И; если хотите, однако, вы можете расположить их сразу друг за другом и сэкономить свои усилия на соединении их проводами позже.

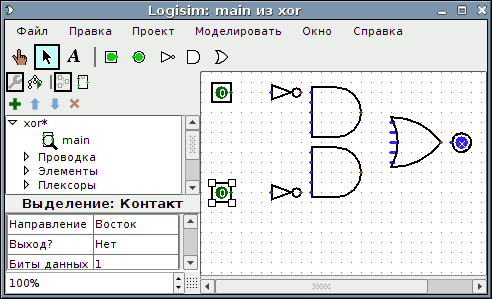

Теперь мы хотим добавить в чертёж два входа х и у. Выберите инструмент Добавить входной контакт () и разместите контакты. Вам также нужно разместить выходной контакт рядом с выходом элемента ИЛИ, используя инструмент Добавить выходной контакт (). (Опять же, я оставляю немного пространства между элементом ИЛИ и выходным контактом, но вы можете разместить их сразу друг за другом.)

Если вы решили, что вам не нравится, где вы разместили что-то, то вы можете выбрать это с помощью Инструмента Правка () и перетащить в нужное место. Или же вы можете удалить его полностью, выбрав Удалить из меню Правка или нажав клавишу Delete.

Когда вы размещаете каждый компонент, вы заметите, что как только компонент размещён, Logisim возвращается к Инструменту Правка, так что вы можете двигать размещённый компонент, или (как мы скоро увидим) соединить компонент с другими, создавая провода. Если вы хотите добавить копию недавно размещённого компонента, то быстрый вызов для этого — нажать Control-D для дублирования выделения. (Некоторые компьютеры используют другие клавиши для меню, такие как клавиша Command на Макинтошах. Вам нужно нажать эту клавишу с клавишей D.)

Далее: Шаг 2: Добавление проводов

Create complex or simple digital logic circuits and test their validity with this intuitive application, using the wide collection of components that it features

What’s new in Logisim 2.7.1:

- Feature: When errors are in a file being loaded, the file is still partially loaded and displayed. If multiple errors are found, each is displayed.

- Feature: In Plexers library, added Select Location attribute to multiplexer, demultiplexer, and decoder.

- Feature: If some components somehow manage to get «off the grid,» they are relocated back onto the grid once they are moved.

- Behavior change: With transistors and transmission gates, a floating value is passed through as floating regardless of the value of gate (including a floating or error gate value).

Read the full changelog

Logisim is an open source computer program that allows you to create and simulate digital logic circuits. It’s a straightforward tool that is aimed for use in schools and universities as it provides the means to create both simple educational circuits, as well as complex ones.

A tool well suited for anyone

Logisim displays a graphical user interface which makes it easy to understand and use if you have basic knowledge in electronics and circuitry. From the main window you are able to access all of its features and tools, and since the app doesn’t even need installing, you’re ready to get started with it immediately after you copy it to your computer.

As you would expect, the workspace is comprised from a generous drawing space, an easy to explore library and a toolbar that contains project simulation commands and configuration options.

Component rich library

Though small in stature, Logisim doesn’t compromise when it comes to components. It contains a large library of tools and components that you need in order to create circuits. They come grouped into categories such as ‘Wiring’, ‘Gates’, ‘Plexers’, ‘Arithmetic’, ‘Memory’, ‘Input/Output’ and ‘Base’, and can be inserted into the canvas area by a simple means of drag and drop.

Each component that you add to the circuit can be repositioned every time it is required and its properties customized accordingly. If at some point you encounter a component you don’t recognize or are unfamiliar with its technical details, Logisim comes with extremely detailed documentation that can help you overcome any issue.

Design and simulate logic circuits

Logisim enables you to effortlessly draw circuits, simulate their use and view color coded wires that can indicate the presence of errors. Moreover, once you’ve successfully created your simulation it can be exported in GIF format and shared with colleagues or inserted into various projects.

With the above in mind and a lot more to discover in the details, Logisim can easily pass for a practical and efficient learning tool.

Атрибуты

Когда компонент выбран, или уже добавлен, комбинации от Alt-0 до Alt-9 меняют его атрибут Биты данных

, а клавиши со стрелками меняют его атрибут Направление

.

- Направление

- Сторона компонента, где должен быть его входной/выходной контакт.

- Выход?

- Определяет, будет компонент выходным контактом или входным. (Заметьте, что если компонент Контакт — входной контакт, то контакт, который выступает в качестве интерфейса в схеме, будет выходом, и наоборот.)

- Биты данных

- Количество битов значения, с которым имеет дело контакт.

- Три состояния?

- Для входного контакта этот атрибут определяет, может ли пользователь заставить контакт подать на выход неопределённые (например плавающие) значения. Этот атрибут имеет дело только с интерфейсом пользователя; он никак не влияет на поведение контакта, когда чертёж схемы использован как подсхема. Для выходного контакта атрибут не влияет ни на что.

- Обращение с плавающими

- Для входного контакта атрибут определяет, каким образом следует рассматривать плавающие значения, когда они приняты на входе, возможно с использованием чертежа как подсхемы. При значении «Не менять» плавающие значения передаются в чертёж как плавающие значения; при значении «Повышать» они преобразуются в 1 до того, как передаются в чертёж схемы; и при значении «Понижать» они преобразуются в 0 до того, как передаются в чертёж схемы.

- Метка

- Текст внутри метки, привязанной к компоненту.

- Направление метки

- Расположение метки относительно компонента.

- Шрифт метки

- Шрифт, которым отрисовывается метка.